シリコン系先進デバイス技術 Silicon-Group Advanced Device

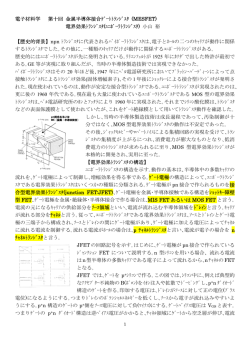

シリコン系先進デバイス技術 Silicon-Group Advanced Device Technology (工学研究院・電気電子工学専攻)須田良幸* 塚本貴広 須田研究室 *連絡先 E-mail: [email protected] 0.70 0.30 30 nm ドレイン電流 (mA/mm) Ge FET, Si FET, 1.はじめに III‐V FET 歪Si FET, Ge MOS Si HBT, III‐V HBT 歪Si MOS Ge sensor Si MOS 半導体成膜法として、現行のガスソー Ge 仮想基板 歪Si ス法(CVD法、GSMBE法)に代えて、資源利 Si 基板 用効率が高く、環境に優しい環境軽負荷 1.図 1 の Si 基板上の歪 Si 層や Ge 層を用いて、Si、歪 Si、 型のスパッタ(エピタキシー)法を開発し、図 Ge、Ⅲ-Ⅴ系の各デバイス(素子)の複合集積化が期待される. さらに、資源が豊富なSiを中心とした、 -1.6 最上曲線 Vgs = -0.5V, +0.5V/ステップ ソース ゲート ドレイン -1.4 : 理論 Si系材料を用いた高速の論理デバイス Au Al Au : 実験 -1.2 真性Si (素子)、高密度メモリ、太陽電池の開発 40 nm -1 p型Si Ge など、環境軽負荷型の次世代半導体素子 -0.8 30 nm -0.6 技術の研究・開発を進めています。 真性Si -0.4 3-4 Ω cm n型Si (100) -0.2 2.Si 系先進素子技術 0 0 -2 -4 -6 -8 -10 ソース対ドレイン電圧 (V) (1) 従来のガスソース法では実現が難し かったトランジスタの高速化ための平坦 図 2.本スパッタで作製した高速型 DCFET の構造と特性. な歪Si膜やSi基板直上のGe膜の形成(Ge Au 仮想基板)をスパッタ法で実現しました。 Ge 15 nm E d E Si 2 nm 4 Ge d nm これによりSi基板上にSi、歪みSi、Ge、 Si 2 nm Ⅲ-Ⅴ系素子を複合集積化した、高速高機 Ge 65 nm 3 能素子の実現が期待されます(図1)。 0.015 -cm 2 p型Si(001) (2) 本スパッタを用いて、高速型の不純 Al 物ドープしたSi1-xGex チャネルを用いた +V 電界効果形トランジスタ(DCFET) (図2)、 図 3.Si/Ge 積層トンネルダイオード(RTD)の作製に世界で 初めて成功. また、平坦Ge膜形成技術(Ge仮想基板)を 40 用いた高速型のSi/Ge共鳴トンネルダイ 30 オード(RTD)の試作に成功しました(図3)。 Al 20 また、ドーパント層の活性化に熱アニー p ‐Si n型Si ルの不要なスパッタ法と室温清浄化技術 10 Al を組み合わせた低コスト太陽電池の作成 0 技術の研究も進めています(図4)。 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 電圧 (V) (3) 大容量化に対応する2端子型で、PN + ダイオード型などの抵抗変化型不揮発性 図 4.スパッタ法で p 活性層を形成した太陽電池の作製. メモリ(ReNVM)を提案し(図5)、スパッタ Au 法を用いて、200 ℃以下の低温プロセス p-Cu O SiO のみを用いた作製にも成功しています。 500 Si/Ge/Si 単一井戸共鳴トンネルダイオード RTD 電流密度 (A/cm2) 400 室温 井戸幅 (nm) lh1 hh1 300 200 ベースライン 100 0 ベースライン 0 0.5 1 1.5 印加電圧 (V) 成膜温度 o 370 C 電流密度 (mA/cm2) o + 390 C o 410 C o 450 C o 490 C o 520 C 700 600 2 x n-SiC 謝辞:本研究の一部は文部科学省科学研 究費補助金基盤(B)、若手研究(B)、およ び、挑戦的萌芽研究の支援を受けて進め ました。 Al n-Si (111) 電流密度 (A/cm2) 500 : (a) 室温SiC/SiOxスパッタ成膜 : (b) 1114K SiCスパッタ成膜 + 1073K SiOx熱酸化 400 300 200 100 0 -100 -6 -4 -2 0 2 4 6 印加電圧 (V) 図 5.提案した 2 端子型不揮発性メモリの構造と特性.

© Copyright 2024