LP2975

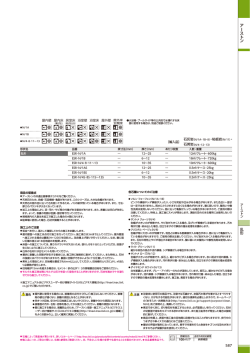

LP2975 MOSFET LDOドライバ / コントローラ 概要 特長 LP2975 LDO コントローラを使用すると、大電流 LDO レギュレー タが簡単に設計できます。外付けの P-FET を使用すれば、自己 消費電流がきわめて小さい、超低ドロップアウトのレギュレータを構 成できます。 ■ 簡単に使用できて外付け部品も少ない ■ 超小型の mini SO-8 パッケージ ■ 1.5%の出力電圧精度 (A グレード品 ) オープン・ループ・ゲインが高いため、優れたレギュレーション性 能とリップル除去性能が得られます。 ■ 低消費のシャットダウン入力 トリミングされた内蔵バンドギャップ基準電圧により、動作温度範 囲の全域にわたり正確な出力電圧が得られます。 ■ 低消費電流 (VIN = 5V のときの代表値は 180μA) ■ シャットダウン時の消費電流 1μA 未満 ■ 広い入力電圧範囲 (1.8 ∼ 24V) ドロップアウト電圧は、外付け FET のサイズを決めると「ユーザ 選択可能」です。動作に必要な最低入出力電圧は、最大負荷 電流に FET の RDS(ON) を乗算した値です。 ■ 電流リミット・アンプを内蔵 ■ 熱暴走保護回路を内蔵 ■ 標準出力電圧は 12V、5V、3.3V INPUT 端子と CURR LIM 端子間にセンス抵抗を入れるだけで、 外付け FET の過電流保護が簡単にできます。 電流センス回路 の検出スレッショルドが 57mVと極めて低いため、 抵抗によるドロッ プアウト電圧と消費電力を最小限に抑えられます。 ■ 外付けの分圧回路により、出力電圧プログラム可能 ■ − 40 ∼+ 125 ℃の接合部温度範囲 出力電圧が 12V、5V、3.3V のものが標準で供給され、25 ℃に おける精度は 1.5%(A グレード )と 2.5%( 標準グレード ) です。 アプリケーション ■ 5V ∼ 3.3V の大電流レギュレータ ■ スイッチング・コンバータの後段のポスト・レギュレータとして ■ 電流制限スイッチ ブロック図 ピン配置図 Surface Mount Mini SO-8 Package Top View For Order Numbers See Table1 of this Document See NS Package Number MUA08A *RSET values are: 208k for 12V part, 72.8k for 5V part, and 39.9k for 3.3V part. © National Semiconductor Corporation DS100034-06-JP 1 LP2975 MOSFET LDOドライバ / コントローラ 2005 年 3 月 LP2975 製品情報 TABLE 1. Package Marking and Ordering Information www.national.com/jpn/ 2 本データシートには軍用・航空宇宙用の規格は記載されていません。 関連する電気的信頼性試験方法の規格を参照ください。 入力電源電圧 ( 動作時 ) + 1.8 ∼+ 24V Current Limitピン ( 最大 ) − 0.3 ∼+ VIN 保存温度範囲 − 65 ∼+ 150 ℃ Comp ピン ( 最大 ) 動作接合部温度範囲 − 40 ∼+ 125 ℃ Gate ピン ( 最大 ) − 0.3 ∼+ VIN + 260 ℃ ON/OFF ピン ( 最大 ) − 0.3 ∼+ 20V 2kV Feedback ピン ( 最大 ) − 0.3 ∼+ 24V リード温度 ( ハンダ付け、5 秒 ) ESD 定格 消費電力 (Note 2) 入力電源電圧 ( 最大 ) − 0.3 ∼+ 2V 内部制限 − 0.3 ∼+ 26V 電気的特性 標準字体で表記される規格値は、TJ = 25 ℃に対するもので、太字は全動作温度範囲に適用されます。特記のない限り、以下の仕様 は VON/OFF = 1.5V、VIN = 15V の場合に適用されます。 Note 1: 絶対最大定格とは、デバイスに破壊が発生する可能性のある限界値をいいます。この定格を超えて動作させているデバイスには、電気的特性は適用さ れません。 3 www.national.com/jpn/ LP2975 絶対最大定格 (Note 1) LP2975 電気的特性 ( つづき) Note 2: LP2975 にはサーマル・シャットダウン回路が内蔵され、ダイ温度の約 150 ℃で作動します。 LP2975 が消費する電力は非常に小さいため、周囲温度が 上昇しても、自己発熱により保護回路が作動することはありません。 Note 3: 25 ℃におけるリミット値は 100%テストされます。 全動作温度範囲にわたるリミット値は、標準統計品質管理 (SQC) 手法によって決められた補正データを 加味して保証されます。 すべてのリミット値は、ナショナル セミコンダクター社の平均出荷品質レベル (AOQL) の計算に使用されます。 代表的なアプリケーション回路 5V - 3.3V @ 5A LDO Regulator * アプリケーション・ヒント参照。 ** 電流制限の必要がない場合は、この抵抗をショートしてください。 www.national.com/jpn/ 4 LP2975 代表的なアプリケーション回路 ( つづき) Adjustable Voltage 5A LDO Regulator * アプリケーション・ヒント参照。 *** 電流制限の必要がない場合は、この抵抗をショートしてください。 5 www.national.com/jpn/ LP2975 代表的な性能特性 特記のない限り、以下の値は TA = 25 ℃、CIN = 1μF、ON/OFF ピンは 1.5V に接続の条件で適用されます。 Minimum Operating Voltage VIN Referred Gate Clamp Voltage ON/OFF Threshold Current Limit Sense Voltage www.national.com/jpn/ 6 LP2975 代表的な性能特性 ( つづき) 特記のない限り、以下の値は TA = 25 ℃、CIN = 1μF、ON/OFF ピンは 1.5V に接続の条件で適用されます。 ON/OFF Pin Current Supply Current ON/OFF Input Resistance Gate Current Gate-Ground Saturation Line Regulation 7 www.national.com/jpn/ LP2975 代表的な性能特性 ( つづき) 特記のない限り、以下の値は TA = 25 ℃、CIN = 1μF、ON/OFF ピンは 1.5V に接続の条件で適用されます。 Leakage Current Load Regulation Controller Gain and Phase Response 参考設計例 RSC = 10mΩ LP2975 コントローラは、あらゆる P チャンネル FET と組み合わせ て使用でき、さまざまなリニア電圧レギュレータを構成できます。 P-FET = NDP6020P 構成可能なすべての電圧と電流の組合わせを記載するのは不 可能なので、いくつかの参考となる設計例とその性能データにつ いて説明します。 ヒートシンク: (VIN ≦ 7V および TA ≦ 60℃として ) 連続したショー トに対する保護が必要な場合、θS-A ≦ 1.5 ℃ /W のヒートシンク が必要です。 一方、連続ショートから保護しなくてよい場合は、 θS-A ≦ 6 ℃ /W のヒートシンクが適当です。 以下に示す性能データは試験の実測値ですが、これを保証する ものではありません。 性能データ : DESIGN #1: VOUT = 5V @ 5A ( 代表的なアプリケーション回 路参照 ) ドロップアウト電圧 「ドロップアウト電圧」とは、レギュレータが出力のレギュレーション を保つために必要な、入出力間の最小電圧差をいいます。出力 電圧が公称値よりも低くなるまでVINを下げることによって測定しま す ( 公称値は、VIN = 5.5V のときに測定した出力電圧です )。 この試験では IL = 5A です。 コンポーネント : CIN = 82μF ( アルミ電解コンデンサ ) COUT = 120μF ( アルミ電解コンデンサ ) CF = 220pF www.national.com/jpn/ ドロップアウト電圧= 323mV 8 DESIGN #2: VOUT = 3V @ 0.5A ( 代表的なアプリケーション回 路の可変電圧レギュレータ参照 ) ロード・レギュレーション 「ロード・レギュレーション」とは、負荷電流が変化した場合の出 力電圧の最大変動量をいいます。負荷抵抗を変えながら、最小 / 最大出力電圧を記録することで測定します。測定された出力電 圧の変動量を公称出力電圧で割り、パーセンテージで表します。 この試験では VIN = 5.6V です。 コンポーネント : CIN = 68μF ( タンタル・コンデンサ ) COUT = 68μF × 2 ( タンタル・コンデンサ ) CC = 470pF R1 = 237kΩ、1% R2 =使用せず RSC = 0.1Ω Feedback ピンを VOUT に接続 P-FET = NDT452P 5mA ≦ IL ≦ 5A: 負荷レギュレーション= 0.012% 0 ≦ IL ≦ 5A: 負荷レギュレーション= 0.135% ライン・レギュレーション 「ライン・レギュレーション」とは、入力電圧が変化した場合の出 力電圧の最大変動量をいいます。入力電圧を変えながら、最小 / 最大出力電圧を記録することで測定します。測定された出力電 圧の変動量を公称出力電圧で割り、パーセンテージで表します。 この試験では IL = 5A です。 ヒートシンク: P-FET のタブを、0.6 平方インチの PC ボード・パター ンにハンダ付け。 出力電圧調整 : このアプリケーションでは、39.9Ω の内蔵抵抗と 並列に R1 の 237kΩ抵抗を接続すれば ( 抵抗値が 34.2kΩに下 がります )、3.3V 部分を 3V に「トリム」ダウンします。 5.4V ≦ VIN ≦ 10V: ライン・レギュレーション= 0.03% 外 付け抵 抗の温 度係 数は、内蔵 抵 抗の温 度 係数 ( 通 常 3000ppm)と異なるため、 このように1 本の抵抗のみを使ってVOUT を調整する方法を推奨するのは、出力電圧を標準電圧 (3.3V、 5V、12V) の 10%以内に設定する場合のみです。それ以外の 出力電圧の設定には後述する 2 本の抵抗を使った方法を参照く ださい。 出力ノイズ電圧 出力ノイズ電圧は、 出力コンデンサと並列に広帯域 AC ボルトメー ター (HP 400E) を直接接続して測定します。この試験では VIN = 6V、IL = 5A です。 ノイズ= 75μV(rms) トランジェント応答 性能データ : 「トランジェント応答」とは、負荷電流が急激に変化した時の出力 電圧の変動をいいます。この試験では VIN = 5.6V です。 ドロップアウト電圧 「ドロップアウト電圧」とは、レギュレータが出力のレギュレーション を保つために必要な、入出力間の最小電圧差をいいます。出力 電圧が公称値よりも低くなるまでVINを下げることによって測定しま す ( 公称値は、VIN = 5V のときに測定した出力電圧です )。こ の試験では IL = 0.5A です。 負荷抵抗は、レギュレータの出力にスイッチを使って接続され、負 荷電流が 0 から 5A へ瞬間的に増大するようになっています。出 力電圧の変動を、オシロスコープの波形写真で次に示します ( 縦 軸は 200mV/division、横軸は 10μs/division)。写真の中央の線 が、レギュレータの公称出力 (5V) です。 ドロップアウト電圧= 141mV 出力は、公称値に対して最大で約− 600mV 変動しています。こ れは、この設計では出力コンデンサとして比較的小さいものが選 ばれているからです。 COUT を大きくすると、トランジェント応答が 大幅に改善されます (Design #2と #3 参照 )。 ロード・レギュレーション 「ロード・レギュレーション」とは、負荷電流が変化した場合の出 力電圧の最大変動量をいいます。負荷抵抗を変えながら、最小 / 最大出力電圧を記録することで測定します。測定された出力電 圧の変動量を公称出力電圧で割り、パーセンテージで表します。 この試験では VIN = 3.5V です。 0 ≦ IL ≦ 0.5A: 負荷レギュレーション= 0.034% ライン・レギュレーション 「ライン・レギュレーション」とは、入力電圧が変化した場合の出 力電圧の最大変動量をいいます。入力電圧を変えながら、最小 / 最大出力電圧を記録することで測定します。測定された出力電 圧の変動量を公称出力電圧で割り、パーセンテージで表します。 この試験では IL = 0.5A です。 3.5V ≦ VIN ≦ 6V: ライン・レギュレーション= 0.017% 出力ノイズ電圧 出力ノイズ電圧は、 出力コンデンサと並列に広帯域 AC ボルトメー ター (HP 400E) を直接接続して測定します。この試験では VIN = 5V、IL = 0.5A です。 Transient Response for 0-5A Load Step ノイズ= 85μV(rms) 9 www.national.com/jpn/ LP2975 参考設計例 ( つづき) LP2975 参考設計例 ( つづき) トランジェント応答 トランジェント応答とは、負荷電流が急激に変化した後の出力電 圧の変動をいいます。この試験では VIN = 3.5V です。 負荷抵抗はレギュレータの出力にスイッチを使って接続され、負荷 電流が 0 から 0.5A へ瞬間的に増大するようになっています。 出 力電圧の変動を、オシロスコープの波形写真で次に示します ( 縦 軸は 20mV/division、横軸は 50μs/division)。 写真の中央の線 が、レギュレータの公称出力 (3V) です。最大変動が約− 50mV であることがわかります。 Transient Response with Output Capacitor Halved 次に、この設計で出力コンデンサをわずか 4.7μF まで小さくし、試 験を行いました ( 下の波形写真参照 )。− 250mV のアンダー シュートがよくわかるように、縦軸は 100mV/division に拡大されて います。さらに重要なのは、トランジェント応答の悪化にともなって 激しいリンギングが発生していることです。 設計者は、この現象 を安定性に欠ける設計の警告サインとしてとらえなければなりませ ん。 Transient Response for 0Ð0.5A Load Step COUT の小型化 一般的にコストを下げ、サイズを小型化できるように、COUT は容 量を小さくすることが求められます。設計ガイドラインでは COUT と して第 1 ポールが 200Hz 以下のものを推奨していますが ( 後述 の出力コンデンサの項参照 )、あらゆる場合に絶対必要な条件で はありません。 COUT を小さくすると、位相マージンが小さくなります。 位相マー ジンが小さくなると、負荷がステップ的に変動した場合の出力のリ ンギングが増加します。COUT を小さくしていくと、最後にはレギュ レータが発振します。 この様子を見るため、Design #2 で 2 個ある 68μF の出力コンデ ンサの一方を取り外し、トランジェント応答試験を再び行いました ( 次の写真参照 )。トータルのオーバーシュートが− 50mV から約 − 75mV へ増加し、トランジェントの第 2「リング」が明らかに大 きくなっています。 Transient Response with Only 4.7 μF Output Cap この設計が安定性に欠けているのは、出力コンデンサが 4.7μF のときのポール fp が 5kHz になるからです ( 出力負荷が 6Ω のと き)。ループのユニティ・ゲイン周波数を解析すると、約 100kHz まで上昇しており、ループ・ゲインがユニティになる前に、FET の ゲート容量ポール fpg によって位相が大きくシフトしていることがわ かります。また、出力電圧が低いため、フィードフォワード・コンデ ンサによる正方向の位相シフト( 位相進み ) が 10° 未満になってい ます。 十分な安定度を得るためには、4.7μF 以上の出力コンデ ンサが必要です。 安定度と位相マージンの詳細については、「アプリケーション・ヒ ント」の項を参照してください。 www.national.com/jpn/ 10 LP2975 参考設計例 ( つづき) DESIGN #3: VOUT = 1.5V @ 6A ( 代表的なアプリケーション回 路の可変電圧レギュレータ参照 ) コンポーネント : CIN = 1000μF アルミ電解コンデンサ COUT = 330μF × 4 OSCON アルミ電解コンデンサ CC =使用せず R1 = 261kΩ、1% R2 = 1.21kΩ、1% RSC = 6mΩ P-FET = NDP6020P ) 連続したショー ヒートシンク: (VIN ≦ 3.3Vと TA ≦ 60 ℃として 「 ト」に対する保護が必要な場合、θS-A ≦ 2.5 ℃ /W のヒートシン クが必要です。一方、連続ショートから保護しなくてよい場合は、 θS-A ≦ 7 ℃ /W のヒートシンクが適当です。 Transient Response for 0Ð6A Load Step 性能データ : ドロップアウト電圧 アプリケーション・ヒント 「ドロップアウト電圧」とは、レギュレータが出力のレギュレーショ ンを保つために必要な、最小の入出力間の電圧差をいいます。 出力電圧が公称値よりも低くなるまで VIN を下げることによって測 定します ( 公称値とは、VIN = 3.3V のときに測定した出力電圧 です )。この試験では IL = 6A です。 ある特定のアプリケーションに最適な FET は、次のような多数の 要因から決まります。 FET の選択 定格電圧 : FET のドレイン - ソース間ブレイクダウン電圧 (BVDSS とも呼ばれる ) は、入力電圧よりも大きくなければなりません。 ドロップアウト電圧= 0.68V ドレイン電流 : ON 状態のドレイン電流は、そのアプリケーション ロード・レギュレーション の最悪ケース ( ショート時 ) の負荷電流よりも大きな値を選ばなけ ればいけません。 「ロード・レギュレーション」とは、負荷電流が変化した場合の出 力電圧の最大変動量をいいます。負荷抵抗を変えながら、最小 / 最大出力電圧を記録することで測定します。測定された出力電 圧の変動量を公称出力電圧で割り、パーセンテージで表します。 この試験では VIN = 3.3V です。 TURN-ON スレッショルド : FET が ON するためのゲート- ソー ス間電圧 ( ゲート・スレッショルド電圧と呼ばれる ) は、非常に重 要です。 多くの FET は、G-S 電圧が 5 ∼ 10V の範囲で使用さ れるよう設計されています。これらを使用できるのは、入力電圧 が十分に高く、ゲートを 5V 以上でドライブできるアプリケーション に限られます。 0 ≦ IL ≦ 6A: 負荷レギュレーション= 0.092% ライン・レギュレーション 最近の FET の中には、TURN-ON スレッショルドが低く( ロジック レベル FET)、ゲート電圧がわずか 3 ∼ 4V で完全に ON するも のがあります。 入力電圧が 5V 以下のアプリケーションではスレッ ショルドが低い FET を、使用しなければなりません。 「ライン・レギュレーション」とは、入力電圧が変化した場合の出 力電圧の最大変動量をいいます。入力電圧を変えながら、最小 / 最大出力電圧を記録することで測定します。測定された出力電 圧の変動量を公称出力電圧で割り、パーセンテージで表します。 この試験では IL = 6A です。 ON 抵抗 : FET の ON 抵抗 (RDSONと呼ばれる ) は、ある負荷 電流で動作するために必要な最小の入出力間電圧が直接決定 されるので、重要なパラメータです (ドロップアウト電圧とも呼ばれ ます )。 3.3V ≦ VIN ≦ 5V: ライン・レギュレーション= 0.033% 出力ノイズ電圧 RDSON は、ゲート- ソース間電圧に大きく依存します。たとえば、 ある FET で VG-S = 5V のときの RDSON は、VG-S が 10V まで増 加すると約 25%低下します。また、RDSON は温度にも依存し、 温度が高くなると増加します。 出力ノイズ電圧は、出力コンデンサと並列に広帯域 AC ボルト・ メーター (HP 400E) を直接接続して測定します。この試験では VIN = 3.3V、IL = 6A です。 LDO 設計のすべてのドロップアウト電圧は、RDSON から次式で 求めます。 ノイズ= 60μV(rms) トランジェント応答 VDROPOUT = ILOAD × (RDSON + RSC) 「トランジェント応答」とは、負荷電流が急激に変化した後の出力 電圧の変動をいいます。この試験では VIN = 3.3V です。 RSC はショート時の電流リミット設定抵抗です ( 「アプリケーション 回路例」 参照 )。 負荷抵抗はレギュレータの出力にスイッチを使って接続され、負荷 電流が 0 から 6A へ瞬間的に増大するようになっています。出力 電圧の変動を、オシロスコープの波形写真で次に示します ( 縦軸 は 50mV/division、横軸は 20μs/division)。写真の中央の線が、 レギュレータの公称出力 (1.5V) です。最大変動が約− 80mV で あることがわかります。 ゲート容量 : 可能な限りゲート容量の小さい FET を選ぶと、次の 2 つの理由から LDO の性能が向上します。 11 www.national.com/jpn/ LP2975 アプリケーション・ヒント ( つづき) 1) LP2975 の Gateピン (FET のゲートをドライブする ) のソースま たはシンクする電流の量には限度があります。そのため、ゲー ト容量が小さくなると、ゲート電圧の変化が速くなります ( トラ ンジェント応答が速くなります )。 IMAX は最大出力電流です。 小電力 (2W 未満 ) のアプリケーション : 低電力回路では、多 くの場合、FET に小型の表面実装タイプを使用できます。 最近 の FET ではセル密度が高くなった ( パッケージが小型化した ) た め、電流容量がパッケージの消費電力の限界値を簡単に超える 可能性があります。そこで、複数の FET を並列に接続し、各部 品の消費電力を分散することも必要です。 2) ゲート容量によって、位相マージンを低下させるポールがルー プ・ゲインに形成されます。 可能であれば、レギュレータ・ ループのクロスオーバー周波数よりもこのポールを高くすべき です ( 後述の「クロスオーバー周波数と位相マージン」の項 を参照 )。 表面実装パッケージ用の「ヒートシンク」は、PC ボードのパター ンとパッケージ自体 ( 直接放熱 ) であることに注意してください。 ゲート容量が大きいと、フィードフォワード・コンデンサで過大な位 相シフトをキャンセルして ( 「フィードフォワード・コンデンサ」の項 を参照 )、ループが不安定になるのを防がなければならない場合 があります。 表面実装デバイスを代表的なPCボードに実装した状態でのθJ-A の値は、その部品用のデータシートに記載されています。 多くの 場合、アプリケーションの既知の値 (PD、TA、TJ) を使って設計 を始め、必要なθJ-A の値を計算するとよいでしょう。この値から FET のタイプが決定でき、場合によっては放熱に必要なヒートシン クも決めることができます。 消費電力 : どのアプリケーションでも、FET による最大消費電力 は次式で求めます。 PMAX = (VIN − VOUT) × IMAX θJ-A = (TJ − TA)/PD(MAX) IMAX は最大出力電流です。回路ショートに耐えるレギュレータを 設計する場合は、電流センス抵抗を使用して、IMAX を安全な値 に制限しなければなりません (「ショート時の電流制限」の項を参 照 )。 設計例 : VIN = 5V、VOUT = 3.3V で、最大負荷電流が 300mA の場合を設計します。この条件を元に、通常の動作中の FET に よる消費電力は、 PD = (VIN − VOUT) × ILOAD FET の消費電力によって、最適なパッケージ・タイプが決まります。 消費電力が 15W 未満のアプリケーションでは、TO-220 パッケー ジが最適です。15W 以上のときは、多くの場合 TO-3 パッケージ が適しています。 から PD = 0.51W になります。TJ の最大許容値は 150 ℃、TA は 70 ℃であるとすると、θJ-A は 157 ℃ /W であることがわかります。 一方、出力の連続ショートに耐えるよう設計する場合は、FET に よる消費電力は最低でも次のようになります。 小電力のアプリケーションでは、表面実装型パッケージを使用す るとサイズとコスト面で有利ですが、消費電力が限界値を超えな いように注意する必要があります。 PD(SC) = VIN × ISC = 5 × 0.33 = 1.65W ( ここでは、要求される 0.3A よりも ISC が 10%大きくなるように、 電流センス抵抗が選ばれているものとしています。 ) 消費電力とヒートシンク 連続ショートに耐えるためには、θJ-A 値として 49 ℃ /W が必要に なります。 LP2975 コントローラは、ほとんどすべての外付け P-FETと組み合 わせて使用できるので、 非常に消費電力の大きなパスFETを使っ た設計も可能です。コントローラには FET を熱暴走から保護する 機能がないので、回路の信頼性を高めるために、放熱設計には 注意を払ってください。 θJ-A 値が求まったので、FET が選択できます。 FET は、計算で 求められたθJ-A 値以下で使用されなければなりません。 大電力 (2W 以上 ) のアプリケーション : 消費電力が 2W 以上 になると、θJ-A 値が小さい、大型パッケージの FET を使用しなけ ればなりません。PD とθJ-A の計算には、前項の式を使用します。 放熱設計の方法 : FET の温度と消費電力には、次式の関係が あります。 θJ-A 値が求まったら、次にヒートシンクを選択するため、θS-A 値 ( ヒートシンク- 周囲間の熱抵抗 ) を求める必要があります。 TJ = (θJ-A × PD) + TA ただし、 θS-A =θJ-A − (θJ-C +θC-S) TJ は、FET の接合部温度 θJ-C は「接合部 - ケース間の熱抵抗」です。このパラメータは、 FET 内部の半導体ダイと、ヒートシンクと接触する FET ケースの 表面との間の熱抵抗を測定して得たものです (θJ-C 値は FET の データシートに記載されています )。TO-220 パッケージの FET の 代表的なθJ-C 値は約 2 ∼ 4 ℃ /W であり、TO-3 パッケージのデ バイスは約 0.5 ∼ 2 ℃ /W です。 TA は、周囲温度 PD は、FET による消費電力 θJ-A は、接合部 - 周囲間の熱抵抗 信頼性の高い設計を行うために、次のガイドラインを推奨します。 1) 最大 ( 最悪ケース ) の FET 接合部温度が、150 ℃を超えな いように設計します。 θC-S は「ケース - ヒートシンク間の熱抵抗」です。この値は、 FET 表面とヒートシンクとの間に存在する熱抵抗を測定して求め ます。θC-S は、パッケージ・タイプとマウント方法によって異なりま す。 TO-220 パッケージをマイカ・インシュレータと熱伝導性グリス を使ってヒートシンクに固定した場合は、θC-S 値は 1 ∼ 1.5 ℃ /W の範囲になります。 TO-3 パッケージを同じ方法でマウントした場 合は、θC-S 値は 0.3 ∼ 0.5 ℃ /W になります。ヒートシンク・メー カーはマウント用ハードウェアも販売しているため、 これについての 最良の情報源はヒートシンクのカタログ (Wakefield、AAVID、 Thermalloy) になります。 2) ヒートシンクは、最悪ケース ( 最大時 ) の TA と PD の値を基 に設計します。 3) 出力のショートに耐えるよう設計する場合は、出力がグラウン ドにショートされた状態で最大消費電力を計算しなければな りません。 PD(MAX) = VIN × ISC ISC は出力ショート時の電流です。 4) 回路ショートを考えなくてよい場合は、動作時の最大消費電 力は次式で求めます。 PD(MAX) = (VIN − VOUT) × IMAX www.national.com/jpn/ 12 ヒートシンクが熱を空気 θS-A はヒートシンク - 周囲間の熱抵抗で、 に放散する効率を表しています。この値が求まったら、その計算 値以下の値を持つヒートシンクを選びます。 通常はヒートシンク・ メーカーのデータシートにθS-A 値が書かれているか、温度上昇対 消費電力のグラフで与えられる場合もあります。 で電流が流れるパターンでの電圧降下により発生する誤差を防 止してください。 外付けコンデンサ ある特定の設計での使用に最適なコンデンサは、電圧と負荷電 流によって決まります ( 出力電圧と電流を変えてテストした回路の 例が、前出の項に記載されています )。 設計例 : 入力が 3.3V、出力が 2.5V、負荷電流が 7A の場合 を設計します。 消費電力は、通常動作時と回路ショート時の両 方を計算します。 設計者が外付けコンデンサを選択するためのガイドを、以下の項 に示します。 通常動作時 : PD = (VIN − VOUT) × ILOAD = 5.6W 入力コンデンサ : 必ずしも必要ではないが、入力コンデンサの使 用を推奨します。 入力のバイパスが良好であれば、レギュレータ が低インピーダンスのソースで動作し、安定性が向上します。ま た、良質の入力コンデンサは、予備のエネルギーを貯蔵してレ ギュレータが利用できるようにすることで、負荷の電流要求量が瞬 間的に増加したときのトランジェント応答も改善されます。 CIN の 容量は、無制限に増加できます。 入力コンデンサの例は、「参 考設計例」の項を参照してください。 出力がグラウンドにショートした場合 : PD(SC) = VIN × ISC = 3.3 × 7.7 = 25.4W ( 通常の 7A よりも ISC が 10%大きくなるよう、電流センス抵抗が 選ばれていると仮定しています。 ) 最大 TA が 70 ℃、最大 TJ が 150 ℃とすると、θJ-A は次のように 計算されます。 出力コンデンサ : 出力コンデンサは、トランジェント応答だけでな く、ループを安定化する ( 補償する ) ために必要です。 負荷電 流の要求が瞬間的に変化したとき、LP2975 の制御ループがパス FET のゲート・ドライブ量を調整するまでの間、出力コンデンサは 電流をソースまたはシンクしなければなりません。一般的な法則と して、出力コンデンサが大きくなれば、トランジェント応答と位相 マージン ( 安定度 ) の両方が向上します。 COUT の値は、無制 限に大きくできます。 θJ-A = (TJ − TA)/PD(MAX) 通常動作時 : θJ-A = (150 − 70) / 5.6 = 14.3 ℃ /W 出力がグラウンドにショートしても動作する設計の場合 : θJ-A = (150 − 70) / 25.4 = 3.2 ℃ /W 14.3 ℃ /W の値は、TO-220 型を使用すれば容易にクリアできま す。必要なθS-A 値を計算します (θJ-C = 3 ℃ /W、θC-S = 1 ℃ / Wとしています )。 出力コンデンサと補償 : LP2975 のループ補償は COUT と、場 合によってはフィードフォワード・コンデンサ CF ( 次項参照 ) によっ て行われます。 θS-A =θJ-A − (θJ-C +θC-S) COUT は、負荷抵抗とともにポール (fp と表記 ) を形成し、 − 20dB/ decade 余分にループ・ゲインのロール・オフ ( 減少 ) を発生させ ます。ポール周波数は次式で計算されます。 θS-A = 14.3 − (3 + 1) = 10.3 ℃ /W 使用できるヒートシンクは、消費電力が 5.6W のときに熱抵抗が 1.0.3 ℃ /W 以下のものです ( メーカーのデータシートのグラフ参 照 )。適当なヒートシンクの例としては、Thermalloy 社の #6100B と IERC 社の #LATO127B5CB があります。 fp = 0.16 / [ (RL + ESR) × COUT] RL は負荷抵抗です。 一方、出力の連続ショートに耐えるよう設計する場合は、θJ-A の 計算結果が 3.2 ℃ /W なので、TO-220 パッケージが使用できな いことがわかります。 COUT は出力コンデンサの容量です。 ESR は COUT の等価直列抵抗です。 一般的なガイドラインとして、fp の周波数は 200Hz 以下でなけれ ばなりません。 負荷電流が大きいときは RL の値が小さくなります ので、COUT を大きくして fp の上昇を防がなければなりません。 θJ-C 値が 1.5 ℃ /W、θC-S 値が 0.4 ℃ /W の TO-3 型を使用する とした場合、必要なθS-A 値は次のように計算されます。 θS-A =θJ-A − (θJ-C +θC-S) θS-A = 3.2 − (1.5 + 0.4) = 1.3 ℃ /W 設計例 : 出力が 5V、1A の場合の最小限の出力コンデンサ容 量を求めます。 θS-A 値が 1.3 ℃ /W 以下なので比較的大型のヒートシンクが必要 になりますが、強制空冷する方法もあります。 fp = 0.16 / [ (RL + ESR) × COUT] から次式が導かれます。 回路ショート電流の制限 COUT = 0.16 / [fp × (RL + ESR) ] 外付け抵抗 (RSC) が 1 本あれば、回路ショート時の電流制限を 容易に実現できます。 RSC の値は次式で計算されます。 計算に使用する値は、fp = 200Hz、RL = 5Ω、ESR = 0.1ΩW ( 仮定値 ) です。 RSC = VCL / ISC COUT を求めると、157μF(もっとも近い標準値は 180μF)となりま す。 ISC は、回路ショート電流です。 VCL は、「電流制限センス電圧」です。 VCL の値は、 「電気的特性」の項にある保証リミット値から 57mV ( 代表値 ) です。 FET による消費電力が最悪ケースの計算を行 う場合は、VCL の公差と RSC の公差 ( 温度変化 ) の両方に注 意しなければなりません。 最大の精度を得るために、INPUT ピンと CURRENT LIMIT ピン を RSC にケルビン接続して、入力電源から FET のソース・ピンま 13 www.national.com/jpn/ LP2975 アプリケーション・ヒント ( つづき) LP2975 アプリケーション・ヒント ( つづき) 出力コンデンサの ESR は、ループ内のポールの 1 つによる位相シ フトの大部分をキャンセルするゼロ (fz) を形成しますので、安定化 の点で非常に重要です。ゼロ周波数は次式で計算されます。 出力電圧の調整 標準の出力電圧の中に希望する電圧がない場合、LP2975 を可 変出力レギュレータとして使用できます ( 代表的なアプリケーション 回路参照 )。外付けの抵抗 R1と R2 ( および 24kΩの内蔵抵抗 ) によって出力電圧が設定されます。 fz = 0.16 / (ESR × COUT) 多くの設計で最良の結果を得るためには、fz の周波数が 5kHz から 50kHz の間になるようにしてください。 COUT と ESR の値は 温度によって変化する場合が多く(アルミ電解コンデンサでは顕著 )、それを考慮しておく必要があります。 R2 は 24kΩの内蔵抵抗と並列に接続されることに注意してくださ い。 COMP ピンとグラウンド間の総抵抗を REQ で表すと、その 値は R2と 24kΩの並列値になります。 設計例 (VOUT = 5V@1A)として、fz が要求を満たすコンデンサ を選択してみます。 ESR の方程式を解くと次のようになります。 REQ = (R2 × 24k) / (R2 + 24k) 出力電圧は次式で表されます。 ESR = 0.16 / (fz × COUT) VOUT = 1.24 [ (R1 / REQ) + 1] fz = 5kHz および 50kHz とすると、18μF のコンデンサの ESR 範 囲は次のようになります。 可変出力電圧設計で考慮すべき重要な点 : 内蔵の 24kΩ 抵抗の公差は約± 20%です。また、その温度係 数は、 R2 に使用する外付け抵抗の TCと大抵は異なっています。 18mΩ ≦ ESR ≦ 0.18Ω Panasonic の HFQ などの、高品質で低 ESR のコンデンサを選ぶ とよいでしょう。一方、 10V/180μF のコンデンサ (#ECA-1AFQ181) は ESR が 0.3Ωあり、設計上の値を外れています。 このような理由から、R2 が 1.2k よりも大きくならないようにしてくだ さい。そうすれば、REQ がほとんど R2 の値で決まり、24k の内 蔵抵抗の公差と TC が出力電圧の精度に与える影響を無視でき るようになります。 安定度の高い設計を行うためには、次のような方法もあります。 1) 有機電解液型 OSCON などの、ESR の低い特殊なコンデン サを使用する。 2) R1 の値は次式で求まります。 R1 = REQ [ (VOUT / 1.24) − 1] 高電圧用コンデンサを使用する。 ESR はコンデンサの物理 的なサイズに反比例して大きくなりますので、同じ容量でも電 圧の高いコンデンサは ( ケース・サイズが大きいため )ESR が 一般的に低くなっています。この例として、 Panasonic の ECA1EFQ181(18μF/25V) は ESR が 0.17Ωであり、設計上の値 におさまります。 外付けコンデンサ ( 可変電圧アプリケーション ) 前出の外付けコンデンサの項で述べた内容は、すべて可変電圧 の場合にも適用できますが、フィードフォワード・コンデンサの値の 求め方だけは異なります。 可変電圧アプリケーションにおけるフィードフォワード・コンデンサ CC( 代表的なアプリケーション回路参照 ) の働きは、前出のフィー ドフォワード・コンデンサの項で述べた機能とまったく同じです。た だし、R1 の値をユーザが決めるため、CC の値を求める計算式 は次のようになります。 3) フィードフォワード・コンデンサを使用する ( 次項参照 )。 フィードフォワード・コンデンサ : どのアプリケーションでも必要と いうわけではありませんが、フィードフォワード・コンデンサ (CF) を 使用すると、多くの設計で位相マージンとトランジェント応答の両 方が向上します。 CC = 1 / (2 π× R1 × fzf) CF によって生まれた位相マージンによって、要求に合った COUT とESR が容易に得られない場合に発生する発振が防止されます ( 前出の項参照 )。 前述のとおり、fzf の最適な周波数は通常 5kHz から 50kHz の間 です。 CF は、ゲート容量によるポールが原因の位相シフトも減少させる ため、ポール周波数が低い ( クロスオーバー以下 ) まま放置した 場合に発生する発振を抑制し、アプリケーションを安定化させま す ( 後出のゲート容量によるポール周波数の項参照 )。 安定度の向上 LP2975 はさまざまなアプリケーションで使用できるので、どのような 設計にも最適なコンポーネントのセットというものはありません。この 項では、特定のアプリケーションで安定度 ( 位相マージン ) を向 上させるように、設計者がコンポーネントを選択するための方法を 説明します。 安定度の高い設計であっても、CF を追加するとループ応答がさ らに向上します ( セトリング時間が短縮されます )。このような理由 から、常にフィードフォワード・コンデンサを使用することを推奨し ます。 ゲート容量 CF は、出力電圧を設定する分圧回路の上側の抵抗に並列に接 続されます ( 代表的なアプリケーション回路参照 )。これによって ループ応答のゼロが形成され、周波数は次のようになります。 設計上で考慮すべき点として、FET のゲート容量によるポール周 波数 ( このポールは fpg と表します ) を確認することが重要です。 fpg はループのクロスオーバー周波数に近いため、位相マージン が減少します。そこで、トータルのゲート容量を計算し、fpg を概 算する方法を説明します。 fzf = 6.6 × 10 − 6 / [CF × (VOUT / 1.24 − 1) ] これを CF について解くと、fzf の方程式は次のようになります。 CF = 6.6 × 10 − 6 / [fzf × (VOUT / 1.24 − 1) ] fp の計算の第一歩は、実効ゲート容量 (CEFF) がどれくらいある かを確認することです。 CEFF の計算式は次のようになります。 ほとんどのアプリケーションでは、fzf を 5kHz から 50kHz の間に設 定しなければなりません。 CEFF = CGS + CGD [1 + Gm (RL / / ESR) ] CGS はゲート - ソース間容量で、次式で計算されます (CISS と CRSS の値は FET のデータシート参照 )。 CGS = CISS − CRSS www.national.com/jpn/ 14 LP2975 アプリケーション・ヒント ( つづき) CGD はゲート -ドレイン間容量で、次の関係があります。 fpg vs. CEFF CGD = CRSS Gm は、FET の相互コンダクタンスです。 FET のデータシートに は、ドレイン電流 (ID と表記 ) がある値のときの順方向相互コン ダクタンスが記載されています。 負荷電流(IL と表記 ) が希望 する値のときの Gm は、次式で計算します。 Gm = Gfs × (IL / ID)1/2 RL は負荷抵抗です。 ESR は、出力コンデンサの等価直列抵抗です。 RL//ESRとは、次式のことです。 (RL × ESR) / (RL + ESR) これらの方程式から、RL によって CEFF が変化することがわかりま す。CEFF の最悪ケース ( 最大 ) の値を求めるには、負荷電流が 最大のとき、すなわち負荷抵抗 RL が最小のときの値を使用しま す。 多くの場合、RL//ESR の値はほぼ ESR で決まります。 グラフからわかるとおり、CEFF の値が 500pF ∼ 2500pF の範囲の ときの fpg の値は 40kHz ∼ 700kHzとなります。fpg が安定度に与 える影響を知るためには、レギュレータ・ループの帯域幅を計算 する必要があります ( 次項、クロスオーバー周波数と位相マージ ン参照 )。 Gate Pin Output Impedance クロスオーバー周波数と位相マージン レギュレータ・ループのクロスオーバー周波数 ( ゲイン曲線が 0dB の線と交差する周波数 ) は fc で表します。この周波数が重要な のは、ここがループ・ゲインがユニティ・ゲイン以下になる点であ り、レギュレータ・ループの使用可能な帯域幅を知ることができる からです。 fc における位相マージン ( あるいはそれがないこと ) によって、レ ギュレータの安定度がわかります。 位相マージンとは、総位相シ フト量を 180° から引いたものです。一般的に、ループが安定する ためには、fc における位相マージンが少なくとも 20° ∼ 30° 必要で す。 fc は次式で概算できます ( パラメータはすべて説明済 )。 ゲート容量によるポール周波数 (fpg) ゲート容量 CEFF によるポール周波数は fpg で表し、次式で概算 できます。 fpg ≅ 0.16 / (RO × CEFF) この方程式は、CF が使用されず、fpg/fc > 1 の場合のものです。 RO は LP2975 の Gate ピンの出力インピーダンスで、Gate ピンは FET のゲートをドライブします。RO は入力電源電圧の関数になっ ていることに注意してください (Gate Pin Output Impedance のグラ フ参照 )。グラフに示すとおり、RO の最小値は VIN = 24V のと きに約 550Ωで、VIN = 3V のときの約 1.55kΩまで上昇していき ます。 ゲート容量のポール周波数 fpg を計算すれば ( 前出の項 )、位相 シフト量の増加分がわかります。 次のグラフに示すように (Phase Shift Due to fpg のグラフ参照 )、fpg が fc に近づくと位相シフトの 増加量が増えます。 発振前に発生する fpg による位相シフトの量は、COUT によるポー ルによって増加する位相シフト量によって左右されます ( 前出の出 力コンデンサの項参照 )。 fpg の方程式を使用すると、RO に対する fpg と CEFF の関係を表 す曲線が得られます (fpgvs.CEFF のグラフ参照 )。 15 www.national.com/jpn/ LP2975 アプリケーション・ヒント ( つづき) Phase Shift Due to fpg フィードフォワード・コンデンサの容量を決定するには、クロスオー バー周波数 fc を最初に計算しなければなりません。 一般的に、 コンデンサによるゼロ周波数は次の範囲になります。 0.2 fc ≦ fzf ≦ 1.0 fc 固定電圧アプリケーションでフィードフォワード・コンデンサの値を 決める方程式は次のようになります。 CF = 6.6 × 10-6/ [fzf × (VOUT/1.24 − 1) ] 可変電圧アプリケーション ( 外付け分圧抵抗を使用する場合 ) で は次のようになります。 CC = 1/(2 π× R1 × fzf) 安定度についてのまとめ この項では、ループ安定度で使用される理論と用語について、 LP2975を使ったアプリケーションを安定化するための情報を中心 に説明します。 このような理由から安定動作の限界が一定しないため、そこから 決定される fpg/fc の正確な数字はありません。ただし、一般的な ガイドラインとして fpg ≧ 3fc を推奨します。 ボーデ線図と位相シフト ループ・ゲイン情報は、ゲイン (dB)と周波数 (Hz) をプロットした ボーデ線図で示される場合がよくあります。 最初の計算後、この値が不適切であると思われる場合は、CEFF を小さくする (FET を変える ) か COUT を大きくするかして、fpg/fc の比を増加させることができます。 ボーデ線図には位相シフト情報も含まれており、ポールとゼロの位 置で分割できます。 これら 2 つの方法に関連して、ループの安定度を向上させるもう 1 つのテクニックとして、フィードフォワード・コンデンサを使用する 方法があります ( 次項のフィードフォワード補償参照 )。これによっ て過度な位相シフトをキャンセルすれば、位相マージンを改善でき ます。 ポール : ポールはゲイン曲線に− 20dB/decade の減衰スロープ を加え、位相の遅れ ( 負の位相シフト ) を発生させます。 1 つのポールは最大− 90° の位相遅れを発生させます (Effects of a Single Pole グラフ参照 )。 0dB における総位相シフトが− 180° になると ( または近づくと )、発振が起こります。そのため、不安 定になる原因は、ゲイン曲線に少なくとも2 つのポールがあるため です。 フィードフォワード補償 レギュレータのループ・ゲインの位相シフトは、fp ( 出力コンデンサ と負荷抵抗によるポール )、fpg (FET のゲート容量によるポール ) のほか、IC の内部コントローラのポール ( 代表特性のグラフ参照 ) によって決まります。 合計の位相シフトが過大な場合、不安定 になります。 ゼロ : ゼロは、ポールとまったく反対の効果を持っています。ゼロ があると、最大+ 90° の位相の進み ( 正の位相シフト ) が発生し ます。また、ゲイン曲線に+ 20dB/decade の増加スロープが加わ ります (Effects of a Single Zero グラフ参照 )。 ループ内にゼロを作り、ポールの影響を抑制するフィードフォワード 補償を行うと、総位相シフトが減少します。 Effects of a Single Pole 適正な周波数にゼロを作るフィードフォワード・コンデンサ CF を取 り付けると、これが実現されます。なお、フィードフォワード・コン デンサはゼロとポールの両方を作ることを指摘しておきます。ゼロ となる周波数は fzf で決まり、ポールの周波数は fpf で決まります。 これらの周波数は次式で求まります。 fzf = 6.6 × 10-6/ [CF × (VOUT/1.24 − 1) ] fpf = 6.6 × 10-6/ [CF × (1 − 1.24/VOUT)] 一般的に、 ループ・ゲインが 1 よりも大きい周波数 ( クロスオーバー 周波数よりも下 ) にゼロが作られようにすると、フィードフォワード・ コンデンサは位相マージンについて大幅な改善をもたらします ( 位 相シフトの減少量が最大になります )。ポールは高い周波数に現 れるようにすると( 高いほど好ましい )、新しいポールによる位相シ フトの大部分が、クロスオーバー周波数以上で発生するようになり ます。そのため、CF により作られるポールとゼロのペアの周波数 が離れていると、ループの安定度を改善する効果が大きくなりま す。 験は、ゲイン曲線が 0dB の線と交差する点 ( この周波数は前述 のとおりfc で表します ) の位相シフト量で行われます。 fzf と fpf についての方程式を見直してみると、VOUT が小さくなる ほど、2 つの周波数が近づくことがわかります。そのため、出力 電圧が高いときには CF の使用が大きな効果をもたらし、VOUT が 1.24V に近づくにつれて効果が小さくなります (CF はまったく影響 しません )。 fc における位相シフトは、ボード線図のすべてのポールとゼロを見 て、各点における位相の遅れと進みに与える影響を合計すると評 価できます。グラフに示すとおり、ポール ( ゼロ ) による位相遅れ ( 進み ) の大部分は、ポール ( ゼロ ) 周波数の 10 倍以内の周波 数で発生しています。 www.national.com/jpn/ 総位相シフト : レギュレータが安定しているかどうかの実際の試 16 一般的に、ループが安定するためには、最低 20° から 30° の位相 マージン ( 総位相シフトと− 180° との差 ) が必要です。 フィードフォワードの効果 : 前項で使用した例を使用して、これ にフィードフォワード・コンデンサ CF を追加します (Improved Phase Margin with Feed-Forward グラフ参照 )。CF が形成するゼロ ( 前 述のとおりfzf) を 10kHz に設定し、CF が形成するポール ( 前述 のとおりfpf) を 40kHz に設定します (VOUT = 5V のときの fpf / fzf の比は 4 倍 )。 Effects of a Single Zero Improved Phase Margin with Feed-Forward 代表的アプリケーションの安定度解析 最初に解析するアプリケーションは、フィードフォワード・コンデンサ のない固定出力電圧レギュレータです (Stable Plot without FeedForward グラフ参照 )。 総位相マージンを評価するため、各ポールとゼロによる個々の位 相シフトは、fp = 200Hz、fz = 5kHz、fzf = 10kHz、fpf = 40kHz、 fc = 50kHz、fpg = 100kHz であるものとして計算します。 Stable Plot without Feed-Forward コントローラのポールによるシフト=− 90° fp によるシフト=− arctan(50k/200) =− 90° fz によるシフト= arctan(50k/5k) =+ 84° fzf によるシフト= arctan (50k/100k) =+ 79° fpf によるシフト=− arctan(50k/40k) =− 51° fpg によるシフト=− arctan(50k/100) =− 27° 6 つの数字を合計すると総位相シフトの計算値が− 95° となって、 位相マージンが 85° となります ( 同じアプリケーションのフィードフォ ワード・コンデンサがない状態に比べて、27° 改選されました )。 この理由から、すべてのアプリケーションでフィードフォワード・コン デンサを推奨します。 常に必要ではありませんが、位相マージン を増加させるとセトリング時間が短縮され、COUT と ESR の温度 変化に対する設計上のガードバンドが増加します。 この例では、COUT と RL で形成されるポールの周波数 ( 前述の とおりfp で表す ) が 200Hz になるように COUT の値が選ばれてい ます。また、COUT の ESR は、ESR と COUT で形成されるゼロ の周波数 (fz で表す ) が 5kHz になるように選ばれています (この 選択は、 このデータシートで前述したガイドラインに従っています )。 平均的なゲート容量を持ち、CGATE によるポール周波数 (fpg で表 す ) は 100kHz であるとみなしています。 発振の原因と対策 LDO アプリケーションで発振の最も多い原因は、出力コンデンサ の ESR です。ESR が高すぎるか、低すぎると、ゼロ (fz) が十分 に位相を進めてくれません。 高 ESR: ESR が高いコンデンサによる影響を説明するため、前 出の例を再び使用し、ESR が 20 倍あるものとします。このように すると、ゼロ fz の周波数が 20 分の 1 になり、5kHz から 250Hz へ移動します (High ESR Unstable without Feed-Forward グラフ 参照 )。 総位相マージンを評価するため、各ポールとゼロによる個々の位 相シフトは、fp = 200Hz、fz = 5kHz、fc = 10kHz、fpg = 100kHz であるものとして計算します。 コントローラのポールによるシフト=− 90° fp によるシフト=− arctan(10k/200) =− 89° fz によるシフト= arctan(10k/5k) =+ 63° fpg によるシフト=− arctan(10k/100k) =− 6° 4 つの数字を合計すると総位相シフトの計算値が− 122° となっ て、位相マージンが 58° となります。このアプリケーションは安定し ていますが、フィードフォワード・コンデンサを使用して改善する余 地があります ( 次項参照 )。 17 www.national.com/jpn/ LP2975 アプリケーション・ヒント ( つづき) LP2975 アプリケーション・ヒント ( つづき) High ESR Unstable without Feed-Forward Low ESR Unstable without Feed-Forward グラフに示すとおり、fz の位置が下がったことで帯域幅が広がり、 クロスオーバー周波数 fc が 200kHz 付近まで押し上げられていま す。プロットを見ると、fp と fz が実質的にキャンセルされ、コント ローラのポールおよび fpg だけが残っています。ところが、fc よりも 低い周波数に fpg がはっきりと現れたために大きな位相シフトが起 こり、位相マージンが非常に小さくなっています。そのため、この アプリケーションは発振するか、安定度が非常に下がっています (トランジェントに対して激しいリンギングが発生します )。 このアプリケーションも、フィードフォワード・コンデンサを追加すれ ば改善されます。CF によってゼロ fzf とポール fpf が線図に追加さ れます (Low ESR Corrected with Feed-Forward グラフ参照 )。 フィードフォワード・コンデンサ CF を追加すると、ゲイン線図にゼロ (fzf) とポール (fpf) が追加されれば、これが改善されます (High ESR Corrected with Feed-Forward グラフ参照 )。 Low ESR Corrected with Feed-Forward この場合、クロスオーバー周波数 fc は約 10kHz になります。 fzf が約 5kHz、fpf が約 20kHz になるように CF を選ぶと ( すなわち VOUT = 5V)、位相マージンが明らかに改善されます。すべての ポールとゼロを計算すると、位相マージンが 9° から 43° に増加して います ( 十分に安定します )。 この場合、fzf が fpg とほぼ同じ周波数になるようCF を選択します (fpg による位相シフトを実質的にキャンセルします )。 追加された ポール fpf が fc 周波数の近くまたは上にあれば、位相遅れが 45° 未満に抑えられ、位相マージンが 45° 以上になります ( 十分に安 定します )。 High ESR Corrected with Feed-Forward 過大なゲート容量 : ゲート容量が大きいとポール fpg の周波数が 下がり、安定度に問題が出ます ( 前述のゲート容量によるポール 周波数の項参照 )。fpg 対 CEFF のグラフに示すとおり、ポール fpg は 40kHz ∼ 500kHz の範囲に入る傾向があります。これでどれ だけの位相シフトが起こるかは、クロスオーバー周波数 fc によって 異なります。 出力コンデンサの ESR 値が高い場合には、ゲート容量の影響が 重要になります (High ESR Unstable without Feed-Forward グラフ 参照 )。ESR 値が高くなると fc が上がり、fpg が曲線上の正のゲ インの部分に入ってきます。fpg が低い周波数へ移動すると( ゲー ト容量が大きい場合 )、この影響が悪い方向へ進みます。 低 ESR: ESR が低い出力コンデンサによって、LDO レギュレー タがどのようにして発振するかを説明するため、同じ例で ESR が 十分に低く、fz がオリジナルの 5kHz から 50kHz に上がっている 状態を考えます。 これが、可能な限りゲート容量の低い FET を選ばなければならな い理由です。ゲート容量が低ければ、出力コンデンサの ESR 値 が高くても余裕ができます。 プロットを見ると (Low ESR Unstable without Feed-Forward グラフ 参照 )、クロスオーバー周波数 fc が 8kHz 付近まで移動している ことがわかります。 fz は fc の 6 倍の周波数ですので、ゼロ fz に よってfcの位相が約9° しか進まず、 これでは十分に安定しません。 www.national.com/jpn/ フィードフォワード・コンデンサ CF を使用すると、fpg による大きな 位相シフトを抑制できますが、その効果は出力電圧によって異なり ます ( 次項参照 )。 18 容量のポール ) による位相シフトと、fz の位置の不適切さ ( すなわ ち出力コンデンサの ESR が公称値を外れている ) に対して寛容 であることがわかります。VOUT が低い場合は、CF がそれほど多 くの補正を行ってくれないため、これらのパラメータを正確に選ば なければなりません。 低出力電圧と CF フィードフォワード・コンデンサ CF は正の位相シフト( 位相進み ) を もたらし、ループ内のさまざまなポールによる過大な位相遅れをあ る程度キャンセルします。しかし、出力電圧によっては CF の効果 が減少することに注意してください。 ポールとゼロのペアが遠く離れていると、互いにキャンセルし合う ことが減るために CF の効果が大きくなります。CF が位相シフトに 与える実質的な効果は、fzf による位相進み ( 正の位相シフト)と fpf による位相遅れ ( 負の位相シフト) の、クロスオーバー周波数 fc における差になります。ポールとゼロの周波数が互いに近づく と、その差が 0 に近づきます。 一般的な設計手順 VIN、VOUT、RL は与えられているとします。 1) COUT に要求される容量を、ポール fp が 200Hz 以下になるよ うに計算します ( 前述の出力コンデンサの項参照 )。この計 算は COUT を決定するという目的であるため、ESR が約 0.1Ω であるとみなしてかまいません。 CF による fc での位相進み量は、fzf / fpf の比とfc に対する fz の 位置の両方で変わります。これをわかりやすくするため、VOUT = 12V、5V、3.3V のそれぞれのときにどれだけ位相が進むかをグ ラフに示します (Phase Lead Provided by CF グラフ参照 )。 重要 : 出力コンデンサに容量の小さなものを使用する場合 (fp > 200Hz)、制御ループの位相マージンは小さくなります。そ の結果、負荷のトランジェントによる出力電圧のリンギング が増大します。出力コンデンサがきわめて小さくなると、発 振が起こります。 CF による fc での位相進み量は、fzf / fpf の比とfc に対する fz の 位置の両方で変わります。これをわかりやすくするため、VOUT = 12V、5V、3.3V のそれぞれのときにどれだけ位相が進むかをグ ラフに示します (Phase Lead Provided by CF グラフ参照 )。 この様子を説明するため、出力コンデンサを通常 (fp = 200Hzと なる値 ) の 1/30 にしたときの標準設計 #2 の波形写真を示してあ ります。 写真に示すとおり、通常の値から外れた値にしても問題 は急には現れず、レギュレータは発振に対して非常に抵抗するこ とがわかります。 Phase Lead Provided by CF 2) 前述のクロスオーバー周波数と位相マージンの項にある方程 式を使用して、クロスオーバー周波数 fc を概算します。 3) 要求される出力コンデンサの ESRを、 ゼロの周波数 fz が 0.5fc になるように計算します ( 前述の出力コンデンサの項参照 )。 4) フィードフォワード・コンデンサ CF の値を、与えられた出力電 圧に対する最大の位相ゲインが得られるゼロ fzf となるように 計算します ( 前述の低出力電圧と CF の項参照 )。 CF の計 算式は、前述のフィードフォワード・コンデンサの項にあります。 有機電解液を使用したタイプの電解コンデンサ (OSCON タイプ ) は ESR が低いのですが、通常のアルミ電解コンデンサに比べて コストが高くなります。 ESR の計算値が使用するコンデンサのものよりも高い場合は、 COUT に直列に抵抗を接続してください。 低電圧設計 : 出力電圧が低い場合の設計では (CF による効果 が小さいため )、COUT と ESR を慎重に選択しないと安定度が低 くなります。 グラフで最も重要な情報は、最大の効果が得られる (もっとも正の 位相シフトが行われる )fzf の周波数範囲です。 VOUT = 12V のとき: 0.1fc < fz < 1.0fc また、FET のゲート容量が大きいと ( 大電流 FET など )、ポール fpg の周波数が低くなって問題が発生する場合があります。 VOUT = 5V のとき: 0.2fc < fz < 1.2fc VOUT = 3.3V のとき: 0.2fc < fz < 1.3fc どちらの場合も、出力コンデンサの容量を大きくし、fp を低い周波 数へシフトする ( 全体のループ帯域幅を減少させる ) と解決しま す。 ESR と CF によってクロスオーバー周波数 fC が変化するの で、計算を何度か行わなければなりません。 CF がもたらす最大の位相シフトが、VOUT によって下がる点も重 要です。 12V では 50° 以上得られますが、3.3V では 30° 以下し か得られません。ここから、出力電圧の高い設計は、fpg( ゲート 19 www.national.com/jpn/ LP2975 アプリケーション・ヒント ( つづき) LP2975 MOSFET LDOドライバ / コントローラ 外形寸法図 特記のない限りinches(millimeters) Surface Mount Mini SO-8 Package NS Package Number MUA08A 生命維持装置への使用について 弊社の製品はナショナル セミコンダクター社の書面による許可なくしては、生命維持用の装置またはシステム内の重要な部品とし て使用することはできません。 1. 生命維持用の装置またはシステムとは (a) 体内に外科的に使 用されることを意図されたもの、または (b) 生命を維持ある いは支持するものをいい、ラベルにより表示される使用法に 従って適切に使用された場合に、これの不具合が使用者に身 体的障害を与えると予想されるものをいいます。 2. 重要な部品とは、生命維持にかかわる装置またはシステム内 のすべての部品をいい、これの不具合が生命維持用の装置ま たはシステムの不具合の原因となりそれらの安全性や機能 に影響を及ぼすことが予想されるものをいいます。 ナショナル セミコンダクター ジャパン株式会社 本社/〒 135-0042 東京都江東区木場 2-17-16 技術資料(日本語 / 英語)はホームページより入手可能です。 www.national.com/jpn/ TEL.(03)5639-7300 その他のお問い合わせはフリーダイヤルをご利用ください。 フリーダイヤル 0120-666-116 本資料に掲載されているすべての回路の使用に起因する第三者の特許権その他の権利侵害に関して、弊社ではその責を負いません。 また掲載内容は予告無く変更されることがありますのでご了承ください。

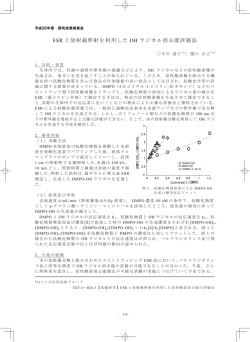

© Copyright 2026