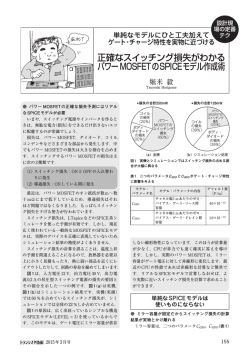

実験室① MOSFETの ゲート抵抗の最適値

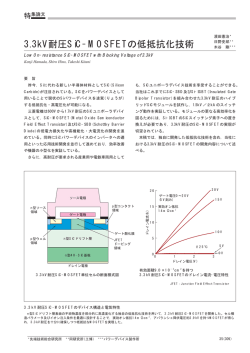

特集 電流ドバッ! 電源・パワエレ実験室 ダメ 実験室① MOSFET の ゲート抵抗の最適値 山本 真義 第 1 章で解説したように,電源回路やパワー回路 を作るときに目指すべきものは次の 3 点です. Masayoshi Yamamoto 直列抵抗の値を最適化することです. ゲート抵抗が大きすぎると,損失 (スイッチング 損失)が増して,性能が低下したり素子が異常に発 熱したりします.小さ過ぎるとサージ電圧が大きく なったり誤 ON が発生したりして故障や誤動作の原 因になるので,大きすぎず小さすぎない値に調整し なければなりません.また,ゲートを駆動する信号 の タ イ ミ ン グ が 適 切 で な い と 過 電 流 が 流 れ て, MOSFET が壊れることがあります. 本章では,ゲート抵抗値の決め方とその理由を説 明します. (1)熱を出さない (2)過電圧,過電流を発生させない (3)ノイズを出さず伝わらせない 多くの電源回路やパワー回路には,MOSFET な どのパワー・トランジスタがスイッチングしていて, 数 A ∼数十 A の大電流を ON/OFF しています.こ のスイッチング回路部は,熱やノイズ,過電圧,過 電流の発生源になっています.まずはこの回路を良 好な状態にする必要があります.第 1 歩はゲートの 評価対象の パワー MOSFET 実験の準備 本章の実験回路を図 1(a)に示します.これをダブ ル・パルス回路と呼びます. モータ・インバータのような典型的なパワー回路の スイッチング特性 (損失)を把握できます.しかも,パ ▶写真 1 パワー MOSFET のスイッチング特性評価に使うダブ ル・パルス回路基板 ゲート抵抗は 0Ω,10Ω,1000Ω の 3 種類用意した VDD ダブル・パルス信号は この端子から入力 IRF740LC (ビシェイ) ゲート抵抗を0Ω,10Ω, 1000Ωの3種類で測定 100μH VGS Vin (400V) IRF740LC (ビシェイ) RG 時間[s] 2.5μ∼2.6μ VDS VDS(Tr2) VGS ID ID(Tr2) 時間[s] 0.15 このターン・オフ直前のドレイン電流が10Aになるように調整する (a)実験回路 (b)各部の電圧・電流 図 1 ゲート抵抗の最適値を求める実験回路 (ダブル・パルス回路と呼ぶ) ゲート抵抗変化の影響実験は,ダブル・パルス回路の ON/OFF 時間を設定して 10 A 電流値でのターン・オン / ターン・オフ波形を確認する 2015 年 1 月号 95 イントロダクション 第2章 元から 熱とノイズが一番出やすい大電 断たなきゃ 流ON/OFFスイッチを最適化! 1 2 3 4 5 6

© Copyright 2024