ダウンロード

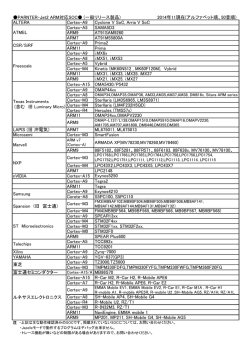

産業機器向けi.MX 6プロセッサ・高速インタフェース 搭載ボードのエコシステム・ソリューション ボ 東京エレクトロンデバイス株式会社 東京 クト ンデ イ 株式会社 村里 優樹 RITAエレクトロニクス株式会社 田中 顕裕 Freescaleの組込み Freescale の組込みCPU CPU i.MX 6シリーズ 6シリーズ ■Specifications - CPU : i.MX 6Quad 4x Cortex-A9, up to 1.2GHz i.MX 6Dual 2x Cortex-A9, up to 1.2GHz i MX 6Dual Lite 2x Cortex i.MX Cortex-A9, A9 up to 1 1.0GHz 0GHz i.MX 6solo 1x Cortex-A9, up to 1.0GHz i.MX 6Solo Lite 1x Cortex-A9, up to 1.0GHz System Control PLL Osc PLL, Clock & Reset ・OpenGL/ES 2.x 3D アクセラレータ with OpenCL EP ・OpenVG 1.1 アクセラレータ - ハードウェア・HDマルチメディア・コーデック ・各種HD1080 各種HD1080 ビデオ デコード/エンコード デ ド/ ン ド ・HD1080p / WUXGA (1920x1200) - オーディオ オ デ オ : I2S、SPDIF I2S SPDIF Rx/Tx、ESAI R /T ESAI - 1Gb Ethernet with IEEE1588 - S-ATA 3Gbps I/F (SSD / HDD)、MIPI-CSI2、HSI、PCIe 2.0、 SDXC、SDIO / MMC4.4 - アナログ回路内蔵 アナ グ回路内蔵 CPU Platform MMC 4 4.4 4 / SDXC Dual / Quad Cortex-A9 UART x5, 5Mbps Smart DMA Timer x3 PWM x4 Watch Dog x2 32KB I-cache per core 32KB D-cache per core NEON per core PTM per core 1MB L2-cache + VFPv3 Power Mgmt Power Supplies Temp Monitor Graphics: OpenGL/ES 2.x, OpenCL/EP, OpenVG 1.x Video Codecs: 1080p30 Internal Memory ROM RAM Security RNG I2C x3, SPI x5 ESAI, I2S/SSI x3 3.3V GPIO Keypad S-ATA & PHY 3Gbps Multimedia - ディスプレイ表示 ・2x Parallel, 2x LVDS, MIPI-DSI or HDMI Connectivity MMC 4.4 / SD 3.0 x3 Secure JTAG IOMUX ■Key Features ■Ke Feat res - マルチコア・アーキテクチャ、1MB L2 キャッシュ - Neon、ベクタ浮動小数点コプロセッサ - 64-ビットLP-DDR2 / DDR3 533MHz、Raw / Managed NAND - ハードウェア・グラフィックス・アクセラレータ ハ ドウ ア グラフィ クス アクセラレ タ 6Quad/6Dual USB2 OTG & PHY USB2 Host & PHY USB2 HSIC Host x2 MIPI HSI Audio: ASRC 2x Imaging Processing Unit S/PDIF Tx/Rx Resizing & Blending Inversion / Rotation Image Enhancement PCIe 2.0 (1-lane) LCD & Camera Interface FlexCAN x2 MLB150 + DTCP TrustZone HDMI & PHY 1Gb Ethernet + IEEE1588 Ciphers MIPI DSI NAND Ctrl (BCH40) Security Ctrl MIPI CSI2 Secure RTC 24-bit RGB, LVDS (x3-8) LP-DDR2, DDR3 / LV-DDR3 x32/64, 533 MHz eFuses 20-bit CSI ・DC-DC Converter、リニアレギュレータ内蔵、温度モニタ Auther / BU or Group Data/Rev Freescaleの電源 Freescale の電源IC IC MMPF0100/MMPF0200 MMPF0100/MMPF0200シリーズ シリーズ MM LDO Regulator DC/DC Converter VGEN1 0.8 – 1.55V, 100mA SW1A/B 0.3 – 1.875V, 2.5A VGEN2 0.8 – 1.55V, 250mA SW1C 0.3 – 1.875V, 2A VGEN3 1 8 – 3.3V, 1.8 3 3V 100mA SW2 0 4 – 3.3V, 0.4 3 3V 2A VGEN4 1.8 – 3.3V, 350mA SW3A 0.4 – 3.3V, 1.25A VGEN5 1.8 – 3.3V, 100mA SW3B 0.4 – 3.3V, 1.25A VGEN6 1.8 – 3.3V, 200mA SW4 0.4 – 3.3V, 1A VREFDDR VIN * 0.5V, 10mA SWBST 5 – 5.15V, 0.6A VSNVS 1 .0– 3.0V, 0.4mA Power Management PWRON, STANDBY, RESET, INT (Fault Detection) I2C Interface OTP Memory MMPF0200 Remove SW1C, SW4 MMPF0200 Reduce SW2 : 2A ⇒1.5A Auther / BU or Group Data/Rev Freescaleの組込み Freescale の組込みCPU CPU QorIQ LS1021Aプロセッサ LS1021Aプロセッサ • • • • • Key Architectural Features: • • • • • ARM AMBA4 MPCore™ Virtualization DDR3L/4 32-bit with ECC support 3-port 3 port GigE with IEEE 1588 2x PCI Express Gen2 Multi-protocol 4-Lane SerDes • PCIe-2, SATA3, SGMII • QUICC Engine – HDLC/TDM/ProfiBUS • EnergyStar support with fast wakeup • 2Gbps IP forwarding Key System Integration Features: • Low-cost NAND/NOR flash systems • Low-cost DRAM systems • USB3 SuperSpeed p p • Audio networking and motor control • QorIQ Trust Architecture and ARM TrustZone support • Alignment with Kinetis/Vybrid portfolio Dual ARM Cortex-A7 cores up to 1.0 GHz ECC protected L1/L2 caches DDR3L/4 up to 1.6GHz Over 5,000 Coremark at under 3.7W (TDP power) Industry best Coremark / mW ratio Outstanding security and IP forwarding High integration reduces BOM costs for targeted applications: Industrial gateways Industrial Automation Printing t g & Imaging ag g HMI M2M, Smart “X” Package & Board: P k Package: Power: Temp: Boards: 525-pin, 525 i 19 19x19mm, 19 0 0.8mm 8 b ballll pitch ~2.8W @1.0GHz Typical -40C (TA) to 105C (Tj) Tower low-cost board Freescale Linux BSPs Auther / BU or Group Data/Rev ハードウェア・デザイン・ガイド Hardware Development Guide Design Checklist i.MX 6 Series Layout Recommendations Requirements for Power Management Avoiding Board Bring-up Bring up Problems Hardware Development Guide Common Hardware Design HW Design Checking List Common Hardware Design HW Design Checking List Hardware requirements for migration DRAM interface requirements for migration EPD controller requirements for migration Common Design Checking Page Schematic Checking Page Layout Checking Page MX6 DRAM Bus Length Check :http://cache.freescale.com/files/32bit/doc/user_guide/IMX6DQ6SDLHDG.pdf :https://community.freescale.com/docs/DOC-93819 :http://cache freescale com/files/32bit/doc/app note/AN4397 pdf :http://cache.freescale.com/files/32bit/doc/app_note/AN4397.pdf Auther / BU or Group Data/Rev RITAエレクトロニクス株式会社 プリント基板商品・実績 産業 / 医療 / 通信分野向け (コンシューマ ( / カーエレクトロニクス/最新LSI) ト /最新 ) RITAエレクトロニクスのメーカー機能 コンサル ティング 回路設計 パターン設計 パタ ン設計 ・シミュレーション コンサル ティング 基板製造 FPGA論理・ソフトウエア設計 実装 実機評価 量産基板 量産実装 パートナーと共に部分/一貫対応も可能。開発期間の短縮や、管理工数の低減などに貢献 1 高速信号対応 1. (メモリバス、高速シリアル伝送) 2. ノイズ対策 3. プリント基板の安定供給 (試作短納期、少量~量産、 特性インピ ダンス、高密度構造対応) 特性インピーダンス、高密度構造対応) RITAエレクトロニクス株式会社について アイカ工業株式会社のプリント配線板事業を包括的に継承した会社で、高品質なパターン設計・ シミュレーション プリント配線板 コンサルティングサービスを提供しています シミュレーション、プリント配線板、コンサルティングサービスを提供しています。 詳しくは同社のホームページ http://www.ritael.co.jp をご参照ください。 D4-140918T-02(T) ©RITAエレクトロニクス株式会社 #6 代表的なボード構成とインタフェースのトレンド DDR4 ①給電系 DQ Q Bus Spee ed 高速化 ②高速パラレル DDR3(1.5V) ~2133Mbps/pin DDR2(1.8V) (1066MH ) (1066MHz) ~800Mbps/pin (400MHz) 低電圧化 DDR1(2.5V) ~400Mbps/pin (200MHz) 2000 2005 2010 ③高速 ③高速シリアル 信号劣化 10~14~28Gbps PCI Express3.0 8Gbps 高速化 シリアルATAIII 6Gbps SDI, CXP USB3.0 5Gbps 開発期間 短縮 60 コストダウン 2000 2005 2010 放射ノイズ増加 55 放 放射ノイズ強度[dB(μV/m)] 伝送 送速度 【協力 協力】 】東京エレクトロンデバイス株式会社 50 45 40 35 30 25 水平偏波[dB(μV/m)] 20 垂直偏波[dB(μV/m)] 15 VCCI classB 10 0 D4-140918T-02(T) 200 400 600 周波数[MHz] 800 1000 ©RITAエレクトロニクス株式会社 #7 高速メモリバス用シミュレーション DQ Bus Spee ed ●タイミングシミュレーション グ DDR3(1.5V) 高速化 パターン図ベースのタイミング検証 ~2133Mbps/pin DDR2-667JESD79-2Fより Parameter DQS falling edge to CK setup time DQS falling edge hold time from CK Address and control input setup time Address and control input hold time DQ and DM input setup time (differential strobe) DQ and DM input hold time (differential strobe) (1066MHz) DDR2(1 8V) DDR2(1.8V) ~800Mbps/pin (400MHz) DDR1(2.5V) DDR1(2 5V) ~400Mbps/pin 低電圧化 Symbol tDSS tDSH tIS(base) tIH(base) Min.time 600 600 200 200 Units ps ps ps ps tDS(base) 100 ps tDH(base) 175 ps CK,CK/ (200MHz) tIS tIH CKE tDSH 2000 2005 2015 2010 tDSS DQS tDS tDH tDS tDH DQ ●プレシミュレーション ●ポストシミュレーション パターン設計のルール決め 最終的な波形の確認 3.0 2.5 Volt 2.0 1.5 1.0 0.5 0.0 0 D4-140918T-02(T) 2 4 6 8 10 Time [ns] 12 14 16 18 20 ©RITAエレクトロニクス株式会社 #11 高速シリアル伝送シミュレーション 光モジュール10~14~28Gbps 光 ジ PCI Express 3.0 8Gbps 伝送速度 2000 CoaXPress シングルエンド 6.25Gbps 6G SDI シングルエンド 6Gbps 高速化 シリアルATAIII 6Gbps USB3.0 5Gbps PCI Express Gen2 5Gbps 3G SDI シングルエンド3Gbps シリアルATAII 3Gbps PCI Express1.1 2.5Gbps シリアルATA 1.5Gbps 2010 2005 ①伝送品質シミ レ シ ン ①伝送品質シミュレーション 2015 ②リタ ンロス規格対応 ②リターンロス規格対応 (HSPICE, IBIS-AMIモデル対応) 1 0.8 0.6 p1 0.4 0.2 0 -0.2 02 -0.4 0 0.3 0.6 0.8 Time (ns) D4-140918T-02(T) ©RITAエレクトロニクス株式会社 #18 プリント基板上のLSIへの電源供給…3つのポイント LSIが動作 定常的な電圧降下 LSI電源端子にノイズ発生 LSI電源端子ノイズの伝播 (ノイズ源) ズ I1 V1 プリント基板 電源供給線の 品質確保 LSI動作不良(ジッタ) 基板からの放射ノイズ (被害者側) 2 1 電源供給線 1´ 不具合 2´ I2 V2 Z11 = V1 I1 Z21 = I2=0 V2 I1 I2=0 1. IRドロップのコントロール 電源パターン起因の定量化や、レギュレータのフィードバックポイントの最適化 2 インプット・インピーダンス(Z11)低減によるLSI電源端子ノイズの低減 2. インプ ト インピ ダンス(Z11)低減によるLSI電源端子ノイズの低減 LSI搭載部位の低インピーダンス設計の実施。コンデンサ定数最適化・合理化 3. トランスファー・インピーダンス(Z21)低減による放射ノイズの低減 コンデンサの最適化等による電源ノイズ伝播の少ないパターン設計の実現 D4-140918T-02(T) ©RITAエレクトロニクス株式会社 #23 ノイズ対策設計 1. ノイズ源を少なくする 1 その他 給電系 筐体 ●信号配線のリターンパス確保 モード変換 ・・・EMIルールチェック ●半導体電源端子の低インピーダンス化 ケーブル 信号配線 LSI ン配置、電源 タ ン設計 ・・・パスコン配置、電源パターン設計 機 機器からの放射の原因のイメージ 放射 2. ノイズの伝導を抑制する ●プレーンのノイズ伝播低減 ・・・プレーン共振解析 EMI抑制ルールチェッカー+電源GND解析ソフトの適用 ノイズ抑制ルール準拠 ノイズ抑制ル ル準拠 D4-140918T-02(T) ノイズ伝搬の低減 ©RITAエレクトロニクス株式会社 #30 お客様向け商品(設計・シミュレーション・基板・コンサルティング) 産業機器向けi.MX 産業機器向けi MX 6 6・高速インタフェース搭載ボードのエコシステム・ソリューション 高速インタフェ ス搭載ボ ドのエコシステム ソリ シ ン ~ 基板開発の合理化(開発期間短縮、対策部品点数や基板層数の削減) ~ 1 高速信号伝送 1. - メモリバス…シミュレーションを活用した設計条件の決定、実測用プローブの活用 - 高速シリアル…接続部位の最適化による信号品質確保とリターンロス規格対応 高速シリアル…接続部位の最適化による信号品質確保とリタ ンロス規格対応 2. LSIへの安定電源供給 - IRドロップ Z11, IRドロップ, Z11 Z21の定量化による対策用部品や基板層数の最適化 3. ノイズ対策 - ノイズ対策ルールに準拠したパターン設計の実施と システム構成時の考慮 ノイズ対策ルールに準拠したパターン設計の実施と、システム構成時の考慮 本資料の全編を御要望の方は、以下へお問合せください 東京 レクト ンデバイス株式会社 東京エレクトロンデバイス株式会社 ( 電話 045-443-4020, [email protected] ) RITAエレクトロニクス株式会社 関東支店 ( 電話 03-5912-2855, [email protected] ) D4-140918T-02(T) ©RITAエレクトロニクス株式会社 #36

© Copyright 2026