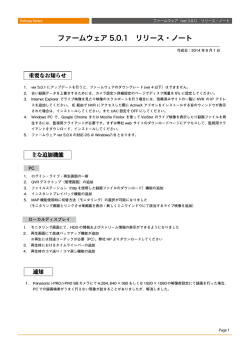

ダウンロード - Freescale Semiconductor

高性能通信プロセッサQorIQのDPAA (デ タ パス アクセラレ ション (データ・パス・アクセラレーション・ アーキテクチャ)の概要 FTF NET F0146 FTF-NET-F0146 Kojij Tsutsui|FAE, | , Technology gy Department p Dec.04.2014 TM External Use 本セッションの目的 • マルチコア・プラットフォームでのパケット処理を効率よく行う為 のデ タパス アクセラレ ション ア キテクチャ(DPAA)が のデータパス・アクセラレーション・アーキテクチャ(DPAA)が QorIQファミリに搭載されております。 • 本セッションでは、DPAAを構成する要素およびCPUコアがどの様 に連携するかを説明します。 • DPAAを活用することで、マルチコア環境で必要とされるパケット 処理のタスクをオフロードすることができ 処理のタスクをオフロ ドすることができ、性能向上に貢献します。 性能向上に貢献します。 TM External Use 1 Agenda • DPAAが必要となる理由 • DPAA構成ブロック − QMan − FMan − BMan − SEC − RMan • • パケットの流れ まとめ TM External Use 2 Agenda • DPAAが必要となる理由 • DPAA構成ブロック − QMan − FMan − BMan − SEC − RMan • • パケットの流れ まとめ TM External Use 3 シングルコアからマルチコアへ • 市場要求: − システム性能のさらなる向上 − 消費電力の制約 • シングルコアでクロック周波数アップ − 性能アップに限界 − 消費電力の点で不利 • マルチコア化 − システム性能の向上および消費電力の点でバランス TM External Use 4 データパスをマルチコアで処理する際の課題/要求事項 マルチコアSoCは、シングルコアSoCと比 べ、パケット処理での要求事項がある − ロードスプレッド/ロードバランス: 受信パケットを複数コアで分散処理 − パケット順序: パケ ト順序 複数コアで並列処理した後、パケット 順序が逆転した場合の対処 順 転 場 処 − パイプライン処理: 1つのパケットをコア、アクセラレー タでパイプライン処理 − ネットワークI/Oの共有: 複数のコア間でネットワ 複数のコア間でネットワークI/Oを共有 クI/Oを共有 − 仮想化 − コア間通信 Hardware Accelerator Core C Core Core Core Core Network I/O Network TM External Use 5 マルチコアでのデータパス処理に必要な機能 • これらの要求事項を満たす為に; − ハードウェアによるキュー管理(輻輳制御も含む) ハ ドウェアによるキュ 管理(輻輳制御も含む) − ネットワークI/Oは、ハードウェアにて受信フレームの解析、 仕分け 宛先へ転送ができること 仕分け、宛先へ転送ができること • 高帯域デ タパスを処理する為に; 高帯域データパスを処理する為に; − 輻輳状態時のフロー制御 Core − バッファ枯渇時のフロ バッファ枯渇時のフロー制御 制御 − ハードウェアによるバッファ管理 Core Core Queue Manager Network I/O Eth Eth Eth TM External Use 6 Core Buffer Manager BDリング vs DPAA DPAAは、従来のBDリ ング方式を置き換える もの: Core • Eth 複数コアがロックレス でキューへ出し入れが 可能 • キュ を複数コアで共 キューを複数コアで共 有 • バッファ管理とキュー 管理を分離 Core Core Core Queue Manager TM External Use 7 Buffer Manager コア(スレッド)毎に ア( ッ )毎 キューへのアクセス用イ ンターフェイスを持つ 他ブロックとの干渉なし Network I/O Eth Eth Eth BDリングはメモリ上 に構築されたデータ ストラクチャ コアはBDリングのポ インタ管理を行う Core Agenda • DPAAが必要となる理由 • DPAA構成ブロック − QMan − FMan − BMan − SEC − RMan • • パケットの流れ まとめ TM External Use 8 QorIQ DPAAを構成するブロック Network & Packet I/O Infrastructure Components Cores Hardware Accelerators RapidIOでの送受信を DPAAに統合 DPAAの基幹ブロック。 SoC内の各ブロック間とのデー タ(パケット)の受け渡しを タ( ケッ ) 受け渡 を キューを用いて一元管理 DPAA RapidIO p Messaging RapidIO Message Manager g (RMan) RMan) and more Ethernet Frame Manager (FMan FMan)) 複数のイーサネットMAC ハードウェアによる受信 フレームのヘッダ解析、 仕分け機能を内蔵 Queue Manager (QMan QMan)) Buffer Manager (BMan BMan)) ハードウェアによるバッ ファ管理(取得/解放) TM External Use 9 Security Engine ((SEC)) 暗号、認証 処理のハー ドウェア・ア クセラレー タ・エンジン Pattern Matching Engine (PME) ビットストリーム中の特定の ビットパターンを検出 ウイルス チェック等で利用 ウイルス・チェック等で利用 QorIQ T4240 DPAA Components TM External Use 10 QorIQ T4240 Agenda • DPAAが必要となる理由 • DPAA構成ブロック − QMan − FMan − BMan − SEC − RMan • • パケットの流れ まとめ TM External Use 11 DPAAインフラストラクチャ: QMan … Queue Manager (QMan): • SoC内の各ブロック(コア、アクセラレータ、Network I/F)間のパケットの受け 渡しはキ 渡しはキューを用い、QManが一元管理 を用 、Q が 元管理 • 各ブロックはQManへアクセスする為のインターフェイスを各々持つ。 − キューはロックレスで共有、リソースの共有化/仮想化が効率的に行える • コアがデキューする際、コア内キャッシュへStash可能 アがデキ する際 ア内キ シ St h可能 − FD、フレームデータ先頭部、 Queue Manager (QMan) コンテキスト情報、他 PME FQD Cache … … … … Hardwa are portals Queuing Engines … QManキューイング管理: − デキュー・スケジューリング デキ スケジ リング − パケット順序の制御 − 輻輳制御/回避 … • FD Memory Software portal Frame Descriptor TM External Use 12 CoreNet To Cores SEC Frame Descriptor FMan FMan QorIQ -- Multi Core and Offload architecture Frame Queue Frame Queue Frame Queue Frame Queue Frame Queue Frame Queue Frame Queue Queue Q Queue Q Dedicated Channel Core7 Frame Queue Dedicated D di t d Channel Data Path Acceleration Architecture PCD Port1 TM External Use 13 Frame Queue Port2 Port3 Frame Queue Frame Queue Dedicated D di t d Channel Frame Manager Port4 Core8 Frame Queue Queue Frame Queue Dedicated Channel Queue Q Pool Channel Queue Q Pool Channel Core3 Core4 Core5 Core6 Queue Core1 Core2 Pseudo Real Time Traffic Dedicated D di t d Channel Frame Queue Queue General Data Plane Traffic Queue Control Plane Traffic Dedicated D di t d Channel 2レベルのキュー WQ1 FQ FQ WQ2 FQ FQ WQ3 FQ FQ WQ4 FQ FQ WQ5 FQ FQ WQ6 FQ FQ WQ7 FQ FQ FD P Portal FQ FQ Cha annel WQ0 フレーム・ディスクリプタ(FD)は、フレーム・ キュー(FQ)に入れられる − FQはFDの順序リスト − QManでの順序制御は、1FQ内で行われる • FQはワーク・キュー (WQ)に入れられる − WQはFQの順序リスト − 1WQ内のFQはすべて同プライオリティ • チャネル: − SoC内各ブロック(コア、アクセラレ SoC内各ブロック(コア アクセラレータ タ、 Network I/O)は自宛てチャネルを持つ − 1つのチャネルは8つのWQから成り、各 WQは相対プライオリティを持つ − デキュー・スケジューリングはチャネル内 WQプライオリティ、スケジューラ・スキー ムにてデキュー順が決定 • ポータル: − 各ブロックがQManへアクセスする為のイ ンターフェイス ンタ フ イ − ポータルは、 QManとデータの受け渡しを 行う為のQMan内 “データ・ストラクチャ” FD FQ 順序制御が必要な フレーム(FD)は1つ のFQへ入れる Bufferr Bufferr • User memory QMan data structures TM External Use 14 チャネルとポータルの種類 H/Wブロック Core n Core0 ロードバランシング ロ ドバランシング 複数コアで負荷分散 via CoreNet DCP (HW Portal) SW Portal SW Portal Dedicated Dedicated via CoreNet Dedicated Pool Channel WQ7 7 WQ6 6 WQ5 5 WQ4 4 WQ3 3 WQ2 2 WQ1 1 WQ0 0 WQ7 7 WQ6 6 WQ5 5 WQ4 4 WQ3 3 WQ2 2 WQ1 1 WQ0 0 FD FQ FD FD FQ WQ7 7 WQ6 6 WQ5 5 WQ4 4 WQ3 3 WQ2 2 WQ1 1 WQ0 0 Channel WQ7 7 WQ6 6 WQ5 5 WQ4 4 WQ3 3 WQ2 2 WQ1 1 WQ0 0 Channel Channel QMan チャネル: − Dedicated Channel:ある特定ブロック宛てチャネル、ある特定ブロックのみがここからデキューする − Pool Channel:不特定多数コア宛てチャネル。複数のコアがここからデキューすることができる、 ロード・バランス用途 • ポ ポータル: タル: − ソフトウェア・ポータル:コアがQManへアクセスする際に使用 − ハードウェア・ポータル:ハードウェア(各アクセラレータ、ネットワークI/O)がQManへアクセスす る際に使用、Direct Connect Portal (DCP)と呼ばれる • キューへアクセスする為のI/F(ポータル)は各ブロック毎に用意されており、ロックレスでQManへア クセス可能(他ブロックとの排他制御は不要) • TM External Use 15 ポータルでのエンキュー/デキュー エンキュー: 送りたい宛先のWQ (FQ)へFDを入れる Rx Tx 10GEC 1GE 1GE ….. PCD デキュー: 自分宛Channelに届いた FQからFDを取り出す SEC FMan1 Core1 SW Portal0 DCP0 DCP2 SP SP Dedicated Core0 Dedicated SW Portal1 EQCR DQRR EQCR DQRR • •• • •• • •• • •• Dedicated Dedicated Pool Channel Channel Channel WQ7 WQ6 WQ5 WQ4 WQ3 WQ2 WQ1 WQ0 WQ7 WQ6 WQ5 WQ4 WQ3 WQ2 WQ1 WQ0 WQ7 WQ6 WQ5 WQ4 WQ3 WQ2 WQ1 WQ0 WQ7 WQ6 WQ5 WQ4 WQ3 WQ2 WQ1 WQ0 Channel WQ7 WQ6 WQ5 WQ4 WQ3 WQ2 WQ1 WQ0 Channel FD FQ FD FD FQ QMan TM External Use 16 L2 Cache Power Architecture™ Core I-Cache パケット順序の制御 D-Cache I-Cache F0P1 • コアがフレームをデキューするにあたり; − Dedicated Channelからのデキュー 常に、同じコアが1つのフロー(FQ)を処理 常に 同じ が ( Q)を処理 コアがパケットを逐次処理している限り、パケット 順序が入れ替わることはない − Pool Channelからのデキュー 複数のコアがデキューする為、各コアでの処理後、 ケット順序が入れ替わる可能性あり パケット順序が入れ替わる可能性あり オーダリングに対処する為のメカニズム: (1) パケット順序の復元 (Order Restoration) − デキ デキュー時に、各フレームにシーケンス番号を割 時に、各フレ ムにシ ケンス番号を割 り当て、コアでの処理後、シーケンス順に並び変 えてからエンキュー (2) パケット順序の維持 (Order Preservation) − 1フロー(1FQ)内のフレームを、同一コアがデ (1FQ)内の レ ムを 同 アがデ キューすることをアシストするデキュー・モード を用意 − コアでの コアでのパケット処理順番そのものを保証 ケット処理順番そのものを保証 F0P2 F1P1 Dedicated Channel L2 Cache L2 Cache Power Architecture™ Core Power Architecture™ Core I-Cache D-Cache I-Cache D-Cache I-Cache F0P1 Ordered packets processed in parallel F0P2 F1P1 P l Channel Pool Ch l L2 Cache L2 Cache Power Architecture™ Core Power Architecture™ Core I-Cache D-Cache I-Cache D-Cache I-Cache F0P1 F0P2 F1P1 TM External Use 17 Pool Channel Ordered packets queued temporally to single processing element • • • • • 輻輳制御はFManとQManが連携動作 ロスレス・フロー制御 輻輳制御 :Tail T il Drop D 輻輳回避 :RED/WRED (Weighted Random Early Discard) Congestion Group(CG): Disca ard Probab bility 輻輳制御/回避 Aggregate Q Occupancy 各フレーム・キューをどのCGグループに属させるか はプログラマブル − Tail Dropは Dropは、CGグループまたは各キュー毎 CGグル プまたは各キュ 毎 − RED/WREDは、CG毎 − − − − − − 全256のCG CGグループ全キューの平均キュー長(Time-aware, Weighted) 3 カラー/WRED カーブはプログラマブル エンキュー・パケットはWREDポリシーで廃棄 瞬間CGグループキュー長 +/- ヒステリシスより、輻 輳メッセージをエンキュー側へ送信 Pauseフレ ム送信によるロスレス・フロ 制御 Pauseフレーム送信によるロスレス・フロー制御 TM External Use 18 CG 1 CG 2 p QMan p Congestion state message p FMan 10G QMI 1G pause 1G 1G 1G Agenda • DPAAが必要となる理由 • DPAA構成ブロック − QMan − FMan − BMan − SEC − RMan • • パケットの流れ まとめ TM External Use 19 ネットワークI/O: FMan To QMan CoreNet Frame Manager (FMan) : • (P4080) 1x10GE MAC + 4xGE MACs • (T4xxx) 2x10GE MAC + 6xGE MACs • Frame Manager (FMan) DMA QMI Policer Keygen Buffer Memory y (Distribution) Parser Classifier To BMan BMI 10GE GE GE GE GE 20 Ingressフレームヘッダを解析しトラフィック判定、 その結果を元に、フレームを適切な宛先キューへ仕 分け − PCDルール-Parsing(解析) / Classification(仕分け)/ Distribution(分配)-に従った仕分け 標準L2/L3/L4プロトコルをサポート ユーザ独自フィールドも定義可 Exact Matchによる特定キューへの仕分け Hashによる複数フレームキューへ振り分け Hashによる複数フレ ムキュ へ振り分け TCP/UDP Tx チェックサム計算 • デュアルレート/3カラー・ポリシング 物理ポート単位での送信レート・リミット BManバッファ・プールから“適正サイズ”のバッファ を取得 • External Use − • • TM FMan内に”Intelligence”を内蔵 FMan内に Intelligence を内蔵 Case Study: High Level Mapping to DPAA CORE CORE CORE portal portal portal Dedicated channel WQ Q7 WQ Q6 Policer WQ Q5 FD FD WQ Q4 WQ Q3 WQ Q2 FQ FD FD WQ Q1 WQ Q0 WQ Q7 WQ Q6 WQ Q5 WQ Q4 WQ Q3 WQ Q2 WQ Q1 WQ Q0 FQ Pool channel FQ FD FD FQ Q FD FQ FD FQ FD FD Hash TOS SCTP UDP (Control) (Dataplane) Eth Prot L2 TOS L3-IP UDP L4 TM External Use n-tuple IP-UDP 21 C bi i exactt match Combining t h + Hash H h DPAAインフラストラクチャ: BMan • バッファ・ポインタの貯蔵領域 − BMan内部RAM(64Pool x 64depth) − 外部メモリ Buffer Manager (BMan) Internal stockpile バッファ ポイ バッファ・ポイ ンタのプール List Engines Software Portals • • ソフトウェアは初期化時にバッファ・プールを 用意 バッファ枯渇時(空きバッファ数が閾値以下)、 ッ ァ枯渇時(空き ッ ァ数 閾値以下)、 割り込みを生成可、これを契機にソフトはバッ ファを補充 TM External Use 22 To Cores CoreNet PME Hardw ware portals Buffer Manager (BMan) : • バッファ・ポインタをハードウェアにて管理 − SoC内のアクセラレータ、ネットワークI/Fは、 BManにリクエストを出してバッファ・ポインタ を取得/解放 SEC FMan FMan Agenda • DPAAが必要となる理由 • DPAA構成ブロック − QMan − FMan − BMan − SEC − RMan • • パケットの流れ まとめ TM External Use 23 ハードウェア・アクセラレータ:SEC5.0 Queue Interface DMA D Job Ring I/F Job Queue Controller RT TIC Descriptor Controllers CHAs Supports protocol processing for the following: • IPSec • 802.1ae (MACSEC) • SSL/TLS/DTLS • 3GPP RLC • LTE PDCP • SRTP • 802.11i (WiFi) • 802.16e 802 16e (WiMax) TM External Use 24 Public Key Hardware Accelerators (PKHA) RSA and Diffie-Hellman (to 4096b) Elliptic curve cryptography (1023b) Data Encryption Standard Accelerators (DESA) DES, 3DES (2K, 3K) ECB, CBC, OFB modes Advanced Encryption Standard Accelerators (AESA) Key lengths of 128-, 192-, and 256-bit ECB, CBC, CTR, CCM, GCM, CMAC, OFB, CFB, and XTS ARC Four Hardware Accelerators (AFHA) Compatible with RC4 algorithm M Message Di Digest tH Hardware d A Accelerators l t (MDHA) SHA-1, SHA-2 256,384,512-bit digests MD5 128-bit digest HMAC with all algorithms Kasumi/F8 Hardware Accelerators (KFHA) F8 , F9 as required for 3GPP A5/3 for GSM and EDGE GEA-3 for GPRS Snow 3G Hardware Accelerators ((STHA)) Implements Snow 3.0 ZUC Hardware Accelerators (ZHA) Implements 128-EEA3 & 128-EIA3 CRC Unit Standard and user defined polynomials Random Number Generator, random IV generation CAAM(SEC4.x / SEC5.x)の特徴 Input Frame: Optional IP Hdr 従来のSECは、入力パ ケットそのままの状態で は、ハンドリングでき なった。 Payload Crypto: Class 1 – such as AES Payload padding Pad N Len Encrypted Pa load Payload padding Pad N Len Cl Class 2 such h as SHA SHA-1 1 SPISeq# Opt IV Payload padding Authenticate Pad N Opt ESN Len CAAMではProtocol Aware となり、暗号、認証の一 となり、暗号、認証の 連の処理(ヘッダ/ト レーラ処理含む)を1コ マンドで指定できる。 → CPUからのオフロード CAAMコマンドのプログラミ ングにて柔軟な処理が可能 ングにて柔軟な処理が可能。 Output Frame: Optional Opt SPISeq# IP Hdr IV Payload padding Esp header TM External Use 25 Pad N ICV Len パケットI/O:RapidIO Message Manager (RMan) RapidIOの送受信をDPAAに統合、SoC内部ではキュー・ベースで転送 26 I$ I$ WQ7 P PME L2$ D$ S SEC I$ Core D$ External Use WQ6 Channel D$ Segmentation Unit Segmentation Unit Channel Frame Manager 1GE 1GE 10GE 1GE 1GE TM WQ5 WQ4 WQ3 WQ2 Reassembly Unit WQ0 WQ1 WQ2 WQ3 WQ4 WQ5 WQ6 WQ7 Classification Unit WQ1 Reassembly Unit WQ0 Classification Unit Segmentation Unit Channel WQ0 WQ1 WQ2 WQ3 WQ4 WQ5 WQ6 WQ7 Reassembly Unit Disassembly Contexts RapidIO O Outbound Trafficc QMan Reassembly Contexts Inbound Rule Matching Classification Unit ARB RapidIO Inbound Traffic RMan Agenda • DPAAが必要となる理由 • DPAA構成ブロック − QMan − FMan − BMan − SEC − RMan • • パケットの流れ まとめ TM External Use 27 IPSec暗号パケットの復号化 • コアは自ポータルからデキュー コアは自ポ タルからデキュ • パケットヘッダを見て、暗号化されている こと、どのSAトンネルのものかを判断 • コアはFDを作り、SEC宛てにエンキュー Core 0 (4) • SECはディスクリプタ内コマンドを実行、パケッ トを復号化、処理結果をメモリへ書き出し • 処理結果を示すFDを生成 。次処理の為コア宛てに エンキュー • コアは自ポータルからデキュー • コアはSEC処理ステータスを確認 • OKならば、復号パケットにL2ヘッダを付加、 FDを作成しFMan送信ポート宛てにエン キュー ・・・ ・・・ Core N (7) SEC (6) • SECは自ポータルからデキュー • SEC処理に必要なディスクリプタを生成 • SAトンネル情報(暗号/認証方式、鍵、等)は、FQ毎に SAトンネル情報(暗号/認証方式 鍵 等)は FQ毎に 予め設定 ・・・ ・・・ ・・・ ((3)) ((5)) QMan • 適正サイズのバッファを要求 • BManよりバッファ取得後、DMAにて受信フレームを外部メモリへ転送 よりバ 得後 受信 ムを外部 転送 • 受信フレームヘッダ部はFManで解析、宛先キューを決定し、エン キュー FMan PCD (1) (8) (2) BMan (9) • バッファの解放 TM External Use 28 • フレーム受信 • FManは自ポータルからデキュー • DMAにてパケットデータを外部メモリから読み出 しポートから送出 まとめ • DPAAは、基本的に、パケット処理をコアから完全にオフロードす る為のものではない • DPAAは、“マルチコア”プラットフォームでのパケット処理を”効率 的“に行う為のしくみ • シングルコアSoCでは考慮する必要がなかった、マルチコアでパ グ ケット処理を行う際の課題をDPAAが解決 − ロード・バランス(複数コアの効率的な利用) − オーダリング管理 − キャッシュの有効活用、など TM External Use 29 TM www.Freescale.com © 2014 Freescale Semiconductor, Inc. | External Use

© Copyright 2026