カタログPDF - Copal Electronics

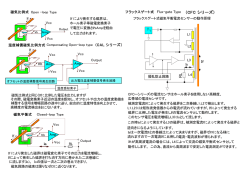

DP7115 DP7115 COPAL ELECTRONICS 32タップ デジタル・ポテンショメータ(DP) 概 要 DP7115 は、機械式のポテンショメータや、可変抵抗 器の代わりとなるプログラム可能なデジタル式ポテン ショメータです。製品の生産ラインで自動化された調 整は理想的と言えます。DP はそれを可能にし、また定 期的な調整を必要としている機器において操作が難し いか又は、危険な場合や遠隔地にあるアプリケーショ ンに適しています。 DP7115には、2つの端子RHとRL間に32タップの抵抗ア レイがあります。3つの入力端子で制御されるアップダ ウンカウンタとデコーダは、ワイパー抵抗RWに接続さ れたタップを決定します。このワイパーは、通常中間 位置に設定されており、電源起動時は、15番目のタッ プに設定されます。このタップ位置は、メモリに保存 されません。 ――― ― DP7115のワイパー制御は3つの入力端子C S 、U/D、 ―――― ―――― ピン接続 ― INC で行います。INC 入力はU/D入力のロジック状態で 決定された方向にワイパーをインクリメントします。 ――― C S 入力はデバイスをセレクトするために利用されま す。電源遮断の前にワイパー位置を保存する時に利用 されます。デジタル・ポテンショメータは3端子の電圧 分圧器又は2端子の可変抵抗器として使用できます。 DPはパラメータ調整、及び信号処理を含む多種多様 なアプリケーションに可変性とプログラムの可能性を 与えます。 特 長 ・32ポジション、直線カーブ、ポテンショメータ ・低消費電力CMOSテクノロジ ・単電源動作:2.5 V - 6.0 V ・インクリメント アップ/ダウン シリアルI/F ・全抵抗値:10 kΩ、50 kΩ、100 kΩ ・ SOIC、TSSOP、MSOPパッケージ ・鉛フリー、ハロゲンフリー/BFRフリー、RoHS対応 アプリケーション ・自動キャリブレーション ・リモートコントロール調整 ・オフセット、ゲイン、ゼロコントロール ・書き換え可能なキャリブレーション ・コントラスト、輝度、ボリュームコントロール ・モーターコントロール、フィードバックシステム ・プログラム可能なアナログ機能 日本電産コパル電子株式会社 2010年10月 – 改訂 9 1 文書番号: DP7115 DP7115 構成 図 1. 回路ブロック図 (概要) 表1. 端子機能 端子名 ―――― INC ― 図 2. 回路ブロック図 (詳細) RL:ローエンドポテンショメータ端子 RLはローエンドポテンショメータ端子です。こ の端子はRH端子よりも低い電圧に接続する必要 はありません。ただし、RL の電圧はVCC以上や GND以下にすることはできません。RHとRLは電 気的に交換することが可能です。 機能 インクリメントコントロール入力 アップダウンコントロール入力 U/D RH GND RW RL ハイエンドポテンショメータ端子 グランド ワイパー端子 ローエンドポテンショメータ端子 チップセレクト ――― CS VCC ――― C S :チップセレクト チップセレクト入力は DP7115 のコントロール 入力を有効とするために利用され、L 状態で有効 電源電圧 ――― ―――― INC:インクリメントコントロール入力 ― ― U/D:アップダウンコントロール入力 ― U/D入力はワイパーの移動方向を制御します。 ――― ―――― U/DがH状態でC S がL状態の時、INC のHからL への遷移でワイパーをRHの方へ動かします。U/ ― ――― ―――― RH:ハイエンドポテンショメータ端子 RHは、ハイエンドポテンショメータ端子です。 この端子はRL端子よりも高電位にする必要はあ りません。ただし、RHの電圧はVCC以上やGND 以下にすることはできません。 ――― ――― ― C S がL状態の時、DP7115はセレクトされU/Dと ―――― ―――― INC 入力に応答します。INC のHからLへの遷移 では、ワイパーをインクリメント・ディクリメ ― ントします (U/D入力と5ビットカウンタの状態 により決定されます) 。このワイパーは機械式 のように振舞い、最後の位置から動きません。 DP7115が電源遮断時、カウンタ位置はリセット されます。電源回復時、カウンタは、中間であ る15番目のタップに設定されます。 RW:ワイパー端子 RWはポテンショメータのワイパー端子です。抵 抗アレイ内での位置はコントロール入力端子 ― ― て、3入力INC 、U/D、C S によって制御されます。 この入力はワイパー位置を選択するためにデコ ードする5ビットのアップダウンカウンタを制 御します。 ―――― D、C S がL状態の時はINC のHからLへの遷移で ワイパーをRLの方向へ動かします。 ―――― ― 動作説明 DP7115は、RH、RLの端子が機械式のポテンシ ョメータの高低の端子に相当し、RW端子はワイ パーに相当するように動作するデジタルのポテ ンショメータです。RHとRLの抵抗器終端を含む 32個のタップがあります。RHとRL端子間には直 列に接続された31個の抵抗アレイがあります。 このワイパー端子は32タップの1つに接続され このINC 入力は、立下りエッジでU/D入力の状態 によって決められた上下の方向にワイパーを動 かします。 ― ―――― となります。C S が H 状態の時は、INC と U/Dの 入力はワイパーポジションに影響や変更を与え ることはありません。 各端子の機能 ―――― 図 3. POT 部の 電気的等価回路 ――― INC 、U/D、C S によって制御されます。ただし、 RWの電圧はVCC以上やGND以下にすることはで きません。 2 DP7115 表2. 動作モード ―――― INC High to Low High to Low High Low X ――― ― CS Low Low Low to High Low to High High U/D High Low X X X 動作 Wiper toward RH Wiper toward RL Store Wiper Position No Store, Return to Standby Standby 図4. ポテンショメータ等価回路 表3. 絶対最大定格 パラメータ 定格 単位 -0.5∼+7 V ――― -0.5∼VCC +0.5 V ―――― -0.5∼VCC +0.5 V -0.5∼VCC +0.5 V -0.5∼VCC +0.5 -0.5∼VCC +0.5 -0.5∼VCC +0.5 V V V -40∼+85 +150 -65∼+150 +300 ℃ ℃ ℃ ℃ 電源電圧 VCC to GND 入力端子 C S to GND INC to GND ― U/D to GND RH to GND RL to GND RW to GND 動作温度 産業用 ( I ) ジャンクション温度 保存温度 端子半田付け (10s max) 「絶対最大定格」を超えたストレスはデバイスに致命的なダメージを与えます。最大定格はストレスの定格のみで あり、推奨動作条件以上の機能動作を意味していません。絶対最大定格の条件に長時間放置しておくと、デバイス の信頼性に悪影響を与えます。 表4. 信頼性特性 記号 パラメータ VZAP (注記1) ESD耐量 ILTH (注記 1, 2) ラッチアップ TDR データ保持 NEND 書き込み可能回数 条件 MIL-STD-883, Test Method 3015 JEDEC Standard 17 MIL-STD-883, Test Method 1008 MIL-STD-883, Test Method 1003 Min 2000 100 100 1,000,000 Typ Max 1. このパラメータは初期において確認済みですが、設計及びプロセスにより変更なる場合があります。 2. ラッチアップ保護回路は、アドレスとデータピンに-1 VからVCC +1 Vにおいて100 mAまで動作します。 3 単位 V mA Years Stores DP7115 表5. DC電気特性 (VCC = +2.5 V∼+6 V) 電源電圧 記号 VCC ICC1 ISB1 (注記 パラメータ 電源電圧 動作電流 4) スタンバイ電流 条件 VCC = 6 V, f = 1 MHz, IW = 0 VCC = 6 V, f = 250 kHz, IW = 0 ――― C S = VCC – 0.3 V ― Min 2.5 - Typ 0.01 Min 2 0 VCC x 0.7 -0.3 Typ - Min Typ 10 50 100 Max 6.0 100 50 1 単位 V μA μA μA ―――― U/D, INC = VCC – 0.3 V or GND ロジック入力 記号 パラメータ IIH 入力リーク電流 (H 入力) IIL 入力リーク電流 (L 入力) VIH1 H レベル入力 (TTL) VIL1 L レベル入力 (TTL) VIH2 H レベル入力 (CMOS) VIL2 L レベル入力 (CMOS) ポテンショメータ特性 記号 パラメータ RPOT 抵抗値 VRH VRL INL DNL RWI IW TCRPOT TCRATIO VN CH /CL /CW fC 公称抵抗値許容差 RH 端子電圧 RL 端子電圧 分解能 積分非直線性誤差 微分非直線性誤差 ワイパー抵抗 ワイパー電流 抵抗温度係数 電圧分圧回路温度係数 ノイズ 端子間容量 カットオフ周波数 条件 VIN = VCC VIN = 0 V 4.5 V ≤ VCC ≤ 5.5 V 2.5 V ≤ VCC ≤ 6 V 条件 -10 Device -50 Device -00 Device 0 0 IW ≤ 2 μA IW ≤ 2 μA VCC = 5 V, IW = 1 mA VCC = 2.5 V, IW = 1 mA 3.2 0.5 0.25 70 150 ±50 100 kHz / 1 kHz Passive Attenuator, 10 kΩ Max 単位 10 μA -10 μA VCC V 0.8 V VCC + 0.3 V VCC x 0.2 V Max 単位 kΩ ±20 VCC VCC % V V % LSB LSB Ω Ω mA ppm/℃ ppm/℃ nV/√Hz pF MHz 1 0.5 200 400 1 ±300 20 8/24 8/8/25 1.7 3. このパラメータは初期において確認済みですが、設計及びプロセスにより変更なる場合があります。 4. ラッチアップ保護回路は、アドレスとデータピンに-1 VからVCC +1 Vにおいて100 mAまで動作します。 5. IW = ソース又は、シンク電流 6. この数値は参考値です。 4 DP7115 表6. ACテスト条件 VCC 電圧範囲 入力パルスレベル 入力立上り、立下り時間 入力基準レベル 2.5 V ≤ VCC ≤ 6 V 0.2 VCC to 0.7 VCC 10 ns 0.5 VCC 表7. AC動作特性 (VCC = +2.5 V∼+6.0 V, VH = VCC, VL = 0 V) 記号 パラメータ Min Typ Max 単位 (注記 7) tCI ――― 100 - - ns tDI ― ―――― 50 - - ns ― ―――― 100 - - ns 250 - - ns 250 - - ns 1 - - μs tID ―――― C S to INC Setup U/D to INC Setup U/D to INC Hold tIL ―――― tIH ―――― tIC ―――― INC LOW Period INC HIGH Period ――― INC Inactive to C S Inactive ――― 100 - - ns tIW ―――― - 1 5 μs tCYC ―――― 1 - - μs tR, tF (注記 8) ―――― - - 500 μs - - 1 ms tCPH tPU, (注記 8) C S Deselect Time INC to VOUT Change INC Cycle Time INC Input Rise and Fall Time Power-up to Wiper Stable 7. これは、温度25 ℃、上記規定の電源電圧における値です。 8. この値は、参考値です。 (注記 9) 図4. ACタイミング 9. A.C.タイミング図のMIは、ワイパーポジションの変化によるワイパー出力での最小変化単位を表しています。 5 DP7115 応用例 (a) 抵抗分圧器 (b) 可変抵抗 (c) 2端子 図6. ポテンショメータ構成 図7. プログラマブル計装アンプ 図8.プログラマブル方形波発振器 (555) 図9. センサー自動リフレッシュ回路 6 DP7115 図10. プログラマブル電装レギュレータ 図11. プログラマブル I-Vコンバータ 図12. 自動ゲインコントロール 図13. プログラマブルバンドパスフィルタ 図14. プログラマブル電装リース/シンク 7 DP7115 パッケージ寸法 SOIC 8, 150 mils 注記: (1) すべての寸法は、mm で表します。角度は度で示します。 (2) JEDEC MS-012 に準拠。 8 DP7115 パッケージ寸法 TSSOP 8, 4.4x3 注記: (1) すべての寸法は、mm で表します。角度は度で示します。 (2) JEDEC MO-153 に準拠。 9 DP7115 パッケージ寸法 MSOP 8, 3x3 注記: (1) すべての寸法は、mm で表します。角度は度で示します。 (2) JEDEC MO-187 に準拠。 10 DP7115 表 8. 製品オーダー情報 Orderable Part Number DP7115VI-10-GT3 DP7115VI-50-GT3 DP7115VI-00-GT3 DP7115YI-10-GT3 DP7115YI-50-GT3 DP7115YI-00-GT3 DP7115ZI-10-GT3 DP7115ZI-50-GT3 DP7115ZI-00-GT3 Resistance (kΩ) 10 50 100 10 50 100 10 50 100 11 Package-Pins Lead Finish SOIC-8 NiPdAu TSSOP-8 NiPdAu MSOP-8 NiPdAu DP7115 オーダーインフォメーション (注記 12) 型式 製品番号 DP 7115 サフィックス V I -10 -G T3 製品番号 テープ&リール T: テープ&リール 3: 3,000/リール パッケージ V: SOIC Y: TSSOP Z: MSOP リードメッキ G: NiPdAu 温度範囲 I: 産業用(-40 ℃∼+85 ℃) 抵抗値 -10: 10 kΩ -50: 50 kΩ -00: 100 kΩ 10. 全てのパッケージはRoHS対応品です。(鉛フリー、ハロゲンフリー) 11. 標準のリードメッキは NiPdAu です。 12. DP7115VI–10-GT3 (SOIC、産業用温度範囲、10 kΩ、NiPdAu、テープ&リール、3,000/リール) を例として表して います。 注意事項 本製品の記載内容は予告なく変更することがあります。 弊社は、特定目的のための製品の適合性の保証は致しません。また、製品や回路の使用から生じるいかなる損害も 負わないものとし、お客様の特別損害、間接損害、付随的損害を含む損害を放棄し、弊社はこれらの責任も負わな いものとします。 弊社のデータシートと仕様書に記載の標準的なパラメータは様々な用途で変化することや、実際の性能は時間の経 過とともに変化する可能性があります。「Typ.値」を含むすべての動作パラメータはお客様のアプリケーションで 十分な検証をお願いします。 弊社は、本資料に関する特許に基づくライセンスやその他の権利を付与しません。 弊社製品は、体内に外科的に埋め込むことを意図したシステムに使用される部品や、生命の維持や支援を意図した 他のアプリケーションや、弊社製品の故障が身体の傷害や死亡の状況を引き起こすかも知れないその他のアプリケ ーションのための使用の認可や、意図、設計はされておりません。 お客様は、弊社が意図しない不正な使用により、直接、間接的に生じた個人の身体傷害、死亡から生じる如何なる 請求、コスト、損害や支出(費用)、合理的な弁護士費用から弊社の役員、従業員、子会社、関連会社や販売店を免 責させ補償しなければなりません。これらが、弊社製品(部品)の設計上、製造上の過失から生じた請求、コスト、 等であっても同様とします。 12

© Copyright 2026