DAC51X2 基板 DAC51X2 for High Resolution Audio DAC with

<編集日:R2 2014.11.1> DAC51X2 基板 DAC51X2 for High Resolution Audio DAC with DUAL PCM51X2 製作マニュアル <注意> 本キットをつかって生じた感電、火災等の一切のトラブルについては、当方は責任を負いませんのでご了承 ください。また、基板、回路図、マニュアル等の著作権は放棄していませんので、その一部あるいは全体を 無断で第3者に対して使用することはできません。 1.はじめに 本基板は TI 社の PCM5102 を使用したハイレゾリューション再生を可能にしたオーディオ用 DAC です。 多くの高性能 DAC、たとえば PCM1794 や ES9018S などが差動出力構成としているのに対して PCM5102 では シングルのステレオ出力となっています。差動出力とすることのメリットは素子内でのコモンモードの出力 変動やノイズが外部の差動アンプによりキャンセルが可能となり、S/N 向上への寄与が期待できます。そこ で、本基板では PCM5102 をモノラル駆動とし差動出力構成とするため、入力データをあらかじめ変換して DAC 素子に送り込んでいる点に最大の特徴をもっています。 また出力に差動アンプを設けることは高出力インピーダンスである PCM5102 自体の出力負荷を下げる効果 もあるのと同時に、オペアンプによる低インピーダンス出力は外来ノイズに対する耐性も向上します。 この DAC においては PCM5102 の特長である MCK(マスタークロック)が不要である点から、Raspberry Pi(以 下 RP)との接続も容易です。そのため、RP の出力と接続しやすいピン配置のコネクタも設けています。 本 基板でハイレゾリューション出力を持つ DAC が容易に構成できると思います。 完成例 差動構成のイメージ 2.機能&仕様 主使用素子 機能 入力 出力 必要電源 基板 表 主な仕様 PCM5102(PCM5101,5100 も使用可能)。 ※パタンレイアウトから PCM512n、PCM514n も搭載可能(n=0,1,2。動作未確認)) 。 ハイレゾ再生可能なステレオ DAC PCM 入力(I2S フォーマット)。入力コネクタ×2 アナログ出力(ステレオ) +3.3V 150mA 以上 、±8~15V 50mA 以上 FR4、70μm 銅箔厚、金フラッシュ、寸法 81.28mm×119.38mm 3.基板端子 3-1.基板端子 下表に基板端子の機能を示します。 No P1 P2 P3 P4 P5 P6 P7 P8 P9 P10 P11 P12 機能 VGND V+ LOUT GND GND ROUT Vdd1 GND Vdd2 SEL GND 表 基板端子機能 説明 備考 OP アンプ用負電源 OP アンプ用アナログ電源(±8~15V 程度) 電源 GND OP アンプ用正電源 左 Ch 出力 オーディオ音声出力 信号 GND 信号 GND 右 Ch 出力 3.3V 電源(DAC 側) ディジタル部電源入力 電源 GND 3.3V 電源(変換ディジタル回路側) 入力選択 P11 を開放 :CN2 を選択(PCM-IN) GND P11 を P12 に接続:CN1 を選択(RaspberryPi-IN) 3-2. コネクタ機能 (1)CN1 CN1 は PCM 信号入力コネクタの1つです。とくに Raspberry Pi TYPE B の P6 とストレートに接続可能なピ ン配置となっています。下表にコネクタ配置を示します。 PIN 1 3 5 7 機能 NC LRCLK DATA GND 表 CN1 コネクタ配置 PIN 機能 2 NC ワードクロック入力 4 BCK データ入力 6 NC GND:信号リターン 8 GND 説明 説明 ビットクロック入力 GND:信号リターン Raspberry Pi の P6 については、部品面にピンを配置した場合の並びを想定しており、Pin1 が「3.3V」にな ります。下図の並びと CN1 の配置が一致するようにコネクタの向きを設定ください。 3.3V LRCK BCK DATA GND GND 図 Raspberry Pi の P6 の機能配置 (2)CN2 CN1 は PCM 信号入力コネクタの1つです。標準的な PCM 信号の入力配置(DATA、LRCK、BCK、SCK)になって います。 表 CN2 コネクタ配置(PCM 入力) PIN 機能 説明 PIN 機能 説明 1 DATA データ入力 2 GND GND:信号リターン 3 LRCLK ワードクロック入力 4 GND GND:信号リターン 5 BCLK ビットクロック入力 6 GND GND:信号リターン 7 SCLK システムクロック入力(MCK) 8 GND GND:信号リターン 9 N.C (*1) 10 N.C (*1) (*1)コネクタの Pin9,10 は 3.3V 電源の共有化に使用します。共有使用する場合は CN2 の直近の「Vdd」と記 されたランドからジャンパー線を接続します。 (3)CN3,4 CN3,4 は PCM5102 へのデータ入力チェック用のコネクタになり、通常は使用しません。本基板のパターン から分かるように、たとえばディジタル回路部の出力のみを使用したい場合や、あるいはディジタル回路部 を使用せずシンプルに PCM5102 のみを使用したい場合などに使います。なおこれらの場合には不要な線の切 断が必要になりますので回路図ならびにパターン図を参照して、作業してください。 表 CN3,4 端子機能(PCM 入出力) PIN 機能 説明 PIN 機能 説明 1 DATA データ入出力 2 GND GND:信号リターン 3 LRCLK ワードクロック入出力 4 GND GND:信号リターン 5 BCLK ビットクロック入出力 6 GND GND:信号リターン 7 SCLK システムクロック入出力(MCK) 8 GND GND:信号リターン 9 N.C (*1) 10 N.C (*1) (*1)コネクタの Pin9,10 は 3.3V 電源の共有化に使用します。共有使用する場合は CN2 の直近の「Vdd」と記 されたランドからジャンパー線を接続します。 3-3.ジャンパー線 (1)SCK-L,SCK-R これは通常は使用しません。PCM5102 の MCK(SCK)入力を強制的に GND に接続したい場合に使用します。 4.部品表 次表に部品表例を示します。 表 品名 抵抗 コンデンサ IC 番号 R1 R2-5 R6-9 R10,11 Ra C1-9 C10-13 Cb Cp IC1,2 IC3 IC4-12 IC13 IC14 IC15,16 規格 炭素皮膜 1/4W 金属皮膜 1/4W 金属皮膜 1/4W 金属皮膜 1/4W チップ抵抗 電解コンデンサ フィルムコンデンサ チップコンデンサ チップコンデンサ ロジック ロジック ロジック ロジック ロジック DAC IC17,18 シングル OP アンプ ハッチング部は基板キットに付属。 部品表(例) 仕様 47kΩ 4.7kΩ 2.4kΩ 100Ω 51Ω 47uF/25V 220pF 1uF 0.1uF 74245 7404 74594 7404 74125 PCM5102 OPA134A など 個数 1 4 4 2 15 9 4 8 26 2 1 9 1 1 2 3216 サイズ 2012 サイズ LVC タイプなど LVC タイプなど AHC タイプなど LVC タイプなど LVC タイプなど PCM5122,PCM5142 なども可(た だし未確認) 2 5.接続例 (1)電源および出力の接続 次図を参照にして接続します。3.3V 電源は変換ディジタル回路側と DAC 側を共通接続としていますが、分離 しても構いません。OP アンプ用の電源は 8~15V 程度で供給します。電源は定電圧化された品質のよいもの を使用してください。 DIGITAL/DAC POWER 3.3V OP-AMP POWER GND -15V GND +15V + RIGHT LEFT - AUDIO OUTPUT + 図 電源および出力の接続例 (2)Raspberry Pi(TYPE B)との接続 下図を参照に接続します。Raspberry Pi から 8P フラットケーブルなどを使用して P6 コネクタより本基板の CN1 に接続します。CN1 を選択するために P11,P12 を接続させます。なお Raspberry Pi から本基板に 3.3V 電源 を供給することも可能とは思われますが、Raspberry Pi 側の電圧レギュレータの過加熱の心配もあるので、 避けたほうがいいでしょう。 8‐10Pケーブル P6コネクタ( 右下がPin1) CN1 選択 図 Raspberry Pi との接続 (2)DAI との接続 本基板は Raspberry Pi 以外にも PCM 出力を持った DAI(Renew FFASRC, Simple DAI for CS8416 等々)と 接続することができます。出力フォーマットは IS2 を選択してください。 下図は Simple DAI for CS8416 との接続例を示しています。 CN2選択 時は開放 10Pケーブル IS2,256fsに設定(すべて開放) 図 Simple DAI for CS8416 との接続 6.基板パターン (1)シルク (2)部品面パターン (3)半田面面パターン 7.編集履歴 R1 2014.10.31 R2 2014.11.1 部品表修正(Cb 追加) 8.付録(動作説明) 本基板の変換ディジタル回路は2つの DAC 素子(PCM5102)のそれぞれに L チャンネルのみのデータあるいは R チャンネルのみのデータを分配して供給する機能をもっています。この回路の動作原理は下図に示すよう に、データを 32BCK 分あるいは 64BCK 分だけシフトしたデータ列を作成し、それらから必要なデータのみを 抜き出して DAC 素子に供給しています。また DAC 素子の出力は差動出力となるように、片側のフレームのデ ータは反転させています。たとえば L チャンネルでは LRCK が LOW レベルのきに L チャンネルデータをそのま ま送出し、LRCK が HIGH レベルのときに L チャンネルを反転(INV)させて送出しています。R チャンネルにつ いても同様です。 図 本基板でのディジタル回路のタイミングチャート 9.回路図(巻末) ©OKIRAKU AUDIO 14 Qh' 5 3 74125 2 4 9 IC14 10 P3 P6 P5 P8 P7 P10 P9 CN1 IDC10 Ra 51 3 Ra 51 5 7 9 9 8 7 6 5 4 3 2 A8 A7 A6 A5 A4 A3 A2 A1 B8 B7 B6 B5 B4 B3 B2 B1 11 12 13 14 15 16 17 18 10 Qh' BCK 74594A IC1 74245 PI-IN 13 12 CN1 5 5V BCK 2 4 6 GND 8 10 P2 P1 P4 P3 P6 P5 P8 P7 P10 P9 1 3 5 7 SRCLR 3.3V LRCK DATA GND 11 10 Qa RCLR Qb Qc RCLK Qd Qe SRCK Qf Qg SRCLR Qh Qh' 11 10 SER Qh' C 8 10 P9 P10 P8 P7 9 P6 P5 7 P4 Ra 51 Cp 13 12 11 10 RCLR RCLK SRCK SRCLR 9 Qa Qb Qc Qd Qe Qf Qg Qh 13 12 11 10 9 Qa RCLR Qb Qc RCLK Qd Qe SRCK Qf Qg SRCLR Qh Qh' 9 16 P10 P9 7 P7 P5 CN4 IDC10 3 15 1 2 3 4 5 6 7 17 SCK-L 18 19 GND SCK 20 9 21 22 15 1 2 3 4 5 6 7 24 25 26 Cp Cp 9 MAST DOUT ATT0 MODE1 ATT1 MODE2 ATT2 FLT DEMP SCK AGND BCK AVDD DIN OUTR LRCK OUTL FMT VNEG XSMT CAPM LDOO CPGND DGND CAPP DVDD CPVDD 14 13 R-DATA 12 C12 220p 11 10 C5 47u 9 R8 2.2k 8 R5 4.7k 7 2 6 1 3 R4 4.7k 5 R11 100 ROUT IC18 4 3 2 1u 1u 1u 1u Cb Cb Cb Cb OPA134 C13 R9 220p 2 GND 2.2k 1 27 28 MAST DOUT ATT0 MODE1 ATT1 MODE2 ATT2 FLT DEMP SCK AGND BCK AVDD DIN OUTR LRCK OUTL FMT VNEG XSMT CAPM LDOO CPGND DGND CAPP DVDD CPVDD 14 3 13 L-DATA 12 C10 220p 11 10 C4 47u 9 R6 2.2k 8 R3 4.7k 7 2 6 Vdd2 C2 47u 1 3 R2 4.7k 5 IC17 OPA134 4 3 2 1u 1u 1u 1u Cb Cb Cb Cb R10 100 LOUT GND C11 R7 220p 4 2.2k 1 DAC 3.3V Vdd2 C1 47u PCM51XX AGNS DIGITAL 3.3V 15 1 2 3 4 5 6 7 OPA POWER Vdd1 Vdd1 V+ C3 47u GND GND V+ C8 47u C6 47u C9 47u C7 47u GND 5 9 V- DAC51X2 for High Resolution Audio DAC with MONAURAL USE PCM5102 74594A IC12 D AGNS IC15 74594A IC11 15 1 2 3 4 5 6 7 28 23 Qh' IC7 27 PCM51XX Ra 51 SCLK 74594A IC10 15 1 2 3 4 5 6 7 J Ra 51 SCLK B P2 Ra 51 BCK IDC10 A 26 Cp 15 Qa RCLR Qb Qc RCLK Qd Qe SRCK Qf Qg SRCLR Qh 9 74594A IC8 9 25 14 8 10 P4 1 SRCK 8 P8 12 14 6 P1 RCLK 24 P6 13 14 4 P2 11 RCLR SER 2 Ra 51 Qa Qb Qc Qd Qe Qf Qg Qh SER 13 12 ATOB G IC14 1 15 1 2 3 4 5 6 7 74594A IC6 1 19 4 23 10 14 Qh' IC3 7404 GND Qa RCLR Qb Qc RCLK Qd Qe SRCK Qf Qg SRCLR Qh 2 22 10 11 11 8 12 R1 47k 9 9 21 P3 IDC10 1 Qh' 74594A IC9 2 74125 20 P1 13 IC2 74245 SEL 9 74594A IC5 7404 74125 IC14 P4 9 10 19 GND 2 P10 P9 Ra 51 7 Qh' BCK 11 18 Ra 51 3 DATA+64BCK P7 Ra 51 5 10 11 12 13 14 15 16 17 18 15 1 2 3 4 5 6 7 SCK-R 14 P8 Ra 51 3 B8 B7 B6 B5 B4 B3 B2 B1 12 Qa RCLR Qb Qc RCLK Qd Qe SRCK Qf Qg SRCLR Qh SER 10 P5 A8 A7 A6 A5 A4 A3 A2 A1 13 17 14 3 P3 P6 11 ATOB G 9 8 7 6 5 4 3 2 15 1 2 3 4 5 6 7 SER 8 P4 1 19 Ra 51 1 IC13 1 SER 6 P1 16 Ra 51 12 14 4 PCM-IN P2 12 SER CN2 2 8 P3 4 DATA+32BCK 14 9 Qa RCLR Qb Qc RCLK Qd Qe SRCK Qf Qg SRCLR Qh SER 13 15 Ra 51 IC13 7404 I 1 IC16 CN3 IDC10 Ra 51 74594A IC4 7404 7404 6 2 IC3 P1 12 IC13 P2 10 IC13 DATA 74125 IC14 4 11 15 1 2 3 4 5 6 7 8 1 12 Qa RCLR Qb Qc RCLK Qd Qe SRCK Qf Qg SRCLR Qh SER 13 7404 9 1 13 LRCK(LJ) 3 LRCK H 13 1 G 6 F 4 E 5 D 2 C 5 B 6 A E F G H I V- J

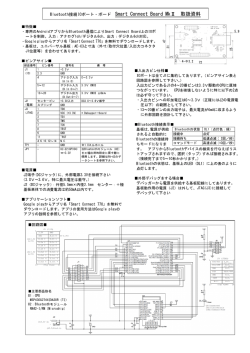

© Copyright 2026