Interface control process toward un

2014/2/4 物理電子システム創造専攻 平成25年度 修士論文発表会 Interface control process toward un-pinned metal/germanium Schottky contact 角嶋・岩井研究室 12M36374 吉原 亮 Tokyo Institute of Technology 1 n型p型MOSFETにおける高チャネル材料 Si Ge elecrton mob. 1600 3900 (cm2/Vs) electron mt:0.19 mt:0.082 effective ml:0.916 ml:1.467 mass (/m0) hole mob. 430 1900 (cm2/Vs) GaAs InP InAs InSb 9200 5400 40000 77000 0.067 0.08 0.026 0.0135 400 200 500 850 Ge hole effective mHH:0.49 mHH:0.28 mHH:0.45 mHH:0.45 mHH:0.57 mHH:0.44 mass (/m0) mLH:0.16 mLH:0.044 mLH:0.082 mLH:0.12 mLH:0.35 mLH:0.016 band gap (eV) 1.12 0.66 1.42 1.34 0.36 0.14 permittivity 11.8 16 12 12.6 14.8 17 Si I. Vurgaftman, et al., J. Appl. Phys., 89, p. 5815 (2001). Table from S. Takagi, IEDM Short course (2011). 移動度バンドギャップを考慮したチャネル選択 n型・・・InGaAs、Ge p型・・・Ge Geは同一材料で構成が期待できるチャネル プロセスの簡略化によりコスト低減が可能 C. H. Lee, et al., IEDM p. 416 (2010). High electron mobility with Ge channel (after Dit reduction process) n型p型 両MOSFETチャネル材料として Geが注目されている 2 Ge MOSFET S/D接合の課題 P, As, Sb (>500oC) の高い拡散係数 ドーパント活性化の不完全性 A. Axmann, et al., Appl. Phys., 12, pp. 173 (1977). S. Mirabella, et al., J. Appl. Phys., 113 031101 (2013). Si Ge EA(eV) D0(cm2/s) EA(eV) D0(cm2/s) P 3.69 1.05×101 2.07 4.38×10-2 As 3.56 3.20×10-1 3.32 1.45×106 Sb 3.96 2.28 1.189×101 Dopant 5.60 C. O. Chui, et al., Appl. Phys. Lett., 83, 3275 (2003). Siにおいても同様であるがGeの場合より深刻な課題 Ge MOSFET S/Dにおいてドーパントの 拡散と活性化の制御が要求される 3 Gate Source/Drain (S/D) の導入 Metal Schottky Lphy Source Drain Drain J. M. Larson, TED, 53, 1048 (2006) Gate Lphy = Leff Metal Conc. mask - 急峻かつ極浅接合 - 短チャネル効果抑制 Source - 低寄生抵抗 - 低熱処理温度プロセス Dopant Conc. Advantages of metal Hard Schottky S/D Gate y position y position Conventional doping Schottky junction Gate Ge p-MOSFETでは多くのmetal Schottky接合(PtGe2, NiGe, etc.) が 報告されている R. Li, et al., EDL, 27, p. 476 (2006). 微細化Ge MOSFETsにおいて metal Schottky接合を用いることが期待されている 4 MetalとGe界面におけるフェルミレベルピニングの課題 A. Dimoulas et al., Appl. Phys. Lett.,89, 252110 (2006). Proposed origins of pinning 金属誘起準位(MIGS) 外因性欠陥 ダングリングボンド 界面の原子配列の乱れ(ラフネス) P. S. Y. Lim, Appl. Phys. Lett.,101, 172103 (2012). Metal/Geは価電子帯付近にフェルミレベルがピニングされる p-MOSFETにとっては望ましいがn-MOSFETでは大きな課題 un-pinnedプロセスの発展が必要である 5 実質的Ge基板un-pinned processの先行研究 Insertion of thin SiN layer M. Kobayashi, et al., J. Appl. Phys., 105, 023702 (2009). SiN厚さに敏感で寄生抵抗とトレードオフの関係 Formation of amorphous Ge layer M. Iyota, et al., Appl. Phys. Lett., 98, 192108 (2011). M. Mitsuhara, et al., JSAP Autumn meeting (2012). プロセス条件に敏感で 熱処理条件に制限がある Schottky S/Dで要求されるun-pinned process条件 界面に絶縁膜を挿入することのないLow fBn (Ohmic) 接合 広く安定したプロセス領域 (電圧, 熱処理温度など) 6 本研究の目的 低抵抗かつ安定性がもとめられる将来のデバイス応用に向けて un-pinned Melal/Geコンタクト作製のガイドラインの提案 1.界面反応を抑制しラフネスが少ないプロセスの構築 2.障壁値変調のための界面不純物導入技術 3.障壁値変調の検証 7 1.界面反応を抑制しラフネスが少ないプロセス の構築 2.障壁値変調のための界面不純物導入技術 3.障壁値変調の検証 8 S/Dメタル選択 S/Dのメタルとして必要な膜の仕様 低抵抗(~200mWcm)(ITRSロードマップ) 耐熱性(界面反応、凝集) 表面モフォロジー 現状CMOSと互換性のある元素 シリサイド系 or ナイトライド系 • NiSi2バルクの比抵抗(34mWcm程度) • 850℃で界面反応抑制、凝集なし 850 oC 20nm L. Knoll et al., IEEE EDL, 31, 350, 2010 本研究ではNiSi2をS/Dメタルとして選択 9 Ge基板上のNiSi2の安定性 R. Yoshihara, et al., ECS 222nd Meeting, ECS Trans.,50, 9, p. 217-221 (2012). XPSによる組成分析 8 set of Si/Ni layers n-Ge(100) sub. Nd = 4x1016cm-3 NiSi2形成のため NiとSiの原子数の 比を2:1とする膜厚 を設定 特長として低温で NiSi2形成可能 Intensity (a.u.) Si(1.9nm) /Ni(0.5nm) NiSi2 NiSi AFMによる表面粗さ (rms) NiGe Ni 2p3/2 h=7940 eV TOA=80o 500 857 800 oC oC 856 855 854 853 852 851 Binding energy (eV) 熱処理温度500 oCにおいて NiGeの反応を抑制しNiSi2を形成 rms Roughness (nm) 積層silicide process 6.0 on n-Ge 4.0 Stacked NiSi2 2.0 0 as depo. 200 300 400 500 600 700 Annealing temperature (oC) 熱処理温度600 oCまで平坦な 表面を実現 350oC~600oCの広い熱処理温度領域で 安定な界面反応の抑制を実現 10 NiSi2のJ-V特性 fBn と ideality factorsの抽出 fBn (eV) 102 101 100 600oC as depo. 10-1 Ideality factor Current density (A/cm2) 0.60 400oC 500oC 10-2 10-3 -1.0 0 Applied voltage (V) 1.0 Stacked NiSi2 0.55 0.50 Ni(5.5nm) 0.45 3.0 Ni(5.5nm) 2.0 1.0 Stacked NiSi2 as depo. 400 500 600 Annealing temperature (oC) 500 oC まで安定したfBn(~0.58 eV)と理想係数(<1.2)を得た 11 11 1.界面反応を抑制しラフネスが少ないプロセス の構築 2.障壁値変調のための界面不純物導入技術 3.障壁値変調の検証 12 Metal/Ge界面にPを導入した積層silicide process Metal/Ge 界面にP原子導入 Si(1.9nm) /Ni(0.5nm) Annealing 7 set of Si/Ni layers n-Ge(100) sub. Nd = 4x1016cm-3 Si(1.9nm) Ni3P(0.68nm) NiSi2 n-Ge(100) sub. Corresponds to P atoms of 4.6x1015 /cm2 最初のNi層の代わりにNi3P層をスパッタで堆積 障壁値変調に適したプロセスとして期待 13 NiSi2:P/GeのTEM断面図 10nm 平坦な表面・界面 界面わずかにコントラストが生じた 凝集による凹凸、界面反応、SiO2の形成 ・界面反応を抑制し平坦な表面・界面を実現 ・界面にコントラストのある1nm層を形成 14 熱処理によるP濃度導入の影響 Backside SIMS深さ方向分布 EDX分析 NiSi2 C Ge Si 500oC 1022 NiSi2 Counts 250 200 10nm Ni 150 Ge Ni O 100 Ge sub. P Ar 50 Ni 0 0 2 4 6 8 10 Energy (keV) 薄い層でGe/P/Ni/Siの混合層形成を確認 P concentration (cm-3) 300 Ge sub. 1021 after 500 oC annealing 1020 1019 before 1018 1017 1016 0 10 20 30 40 50 60 Depth (nm) 熱処理に伴い不純物が拡散 依然として界面に高濃度のPが存在 界面にある不純物と熱処理に伴う基板への不純物拡散 により障壁値変調に期待 15 1.界面反応を抑制しラフネスが少ないプロセス の構築 2.障壁値変調のための界面不純物導入技術 3.障壁値変調の検証 16 P導入によるGe diodeの電流特性の変化 30 20 500oC 600oC Si(1.9nm) /Ni(0.5nm) 400oC 10 0 P incorporation as depo. n-Ge sub. -10 n-Ge (100) (Nd=4x1016cm-3) -20 -30 -1.0 -0.5 0 0.5 Anode voltage (V) 1.0 Current density (A/cm2) Current density (A/cm2) without incorporation 30 20 n-Ge (100) 600oC (Nd=4x1016cm-3) 500oC 10 0 as depo. -10 Si(1.9nm) /Ni(0.5nm) -20 -30 -1.0 400oC 300oC Ni3P (0.68nm) -0.5 0 n-Ge sub. 0.5 1.0 Anode voltage (V) 吉原亮.et al 2012年秋季応用物理学会 Pを導入することで300 oC以上の熱処理温度においてn型Ge でオーミック特性を得ることができた 17 600 oCまで安定したオーミック特性を示した P導入によるコンタクト抵抗の抽出 2.0 1.5 1.0 0.5 0.0 -0.5 -1.0 -1.5 -2.0 -1.0 600oC 30mm 300oC 700oC 200oC 800oC as-sputtered -0.5 0.0 0.5 Voltage (V) 1.0 Contact resistance (Wcm2) Current (mA) 60mm CTLM (circular transmission line model) 10-1 n-Ge (4x1016cm-3) 10-2 10-3 200 300 400 500 600 700 Annealing temperature (oC) 熱処理温度依存性がほとんどない 安定したコンタクト抵抗が得られた 18 コンタクト抵抗から抽出したfBn TE q N E00 2 m s TFE FE kT E00 の場合TFEが支配的に qfBn fn qfn E00 E00 c cosh coth exp qA T qfBn fn kT kT E00 cothE00 kT kT k E00 n-Ge: Nd = 1x1018 cm-3 c 8.0 103 Wcm 2 において fBn 0.44 eV ※不純物なしのNiSi2/Ge:fBn 0.58 eV Contact resistance (Wcm2) Ng, K.K. et al., IEEE Trans. Electron Devices, 37, 1535-1537 (1990). 101 100 Nd = 1x1018cm-3 10-1 10-2 10-3 10-4 10-5 0.3 0.4 0.5 0.6 Schottky barrier height fBn (eV) 電気的に障壁値が変調したと示唆される 19 Intensity (a.u.) XPSによるGe基板バンド曲がりの観測 P incorporation Ge 2p3/2 spectra h=7940 eV TOA=80o 500 oC 1min TOA=80o without incorporation NiSi2 10nm Ge h=7940eV IMFP(l)~10nm 0.3 eV 0 distance from surface Ge (3l~36nm) (3l~30nm) Z 1219 1218 1217 1216 Binding energy (eV) 吉原亮.et al 2013年春季応用物理学会 Ge基板のバンド曲がりの変化により スペクトルがシフトしたと考えられる s NiSi2 only Ge 2p3/2 s,P with P incorporation BE Pの導入により表面電位が増加し un-pinを実現 20 まとめ 目的 un-pinned Metal/Geコンタクトを実現する ガイドラインの提案 1.平坦な表面・界面をTEMにより確認した 2.界面に不純物を導入し300℃~600℃で安定した オーミック特性とコンタクト抵抗を得た 3.コンタクト抵抗とXPSから障壁値の変調を確認した 界面反応を抑制し 広い熱処理温度領域で安定したコンタクト抵抗を示す un-pinned Metal/Geコンタクトのガイドラインを提案できた 21

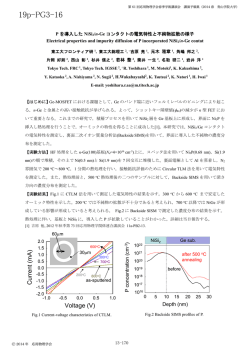

© Copyright 2026