キーデバイス②… NAND型フラッシュ・メモリ

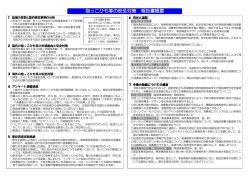

第1部 使えば使うほど壊れていく… 超定番不輝発メモリの基礎知識 3章 第 キーデバイス②… NAND型フラッシュ・メモリ 麻生 浩一郎,宇都宮 厚,長尾 武文 VCCQ VSSQVCC VSS ステータス・レジスタ I/O制御回路 カラム・デコーダ データ・レジスタ コマンド・レジスタ 論理制御 制御回路 RY/BY RY/BY 高電圧生成 ロウ・アドレス・ デコーダ センス・アンプ CE CLE ALE WE RE RE WP DQS DQS ロウ・アドレス・ バッファ・デコーダ DQ7 DQS DQS カラム・バッファ アドレス・レジスタ ⋮ ∼ DQ0 列デコーダ メモリ・セル・ アレイ 行デコーダ 昇圧回路 図 1 NAND 型フラッシュ・メモリ IC の内部回路ブロック NAND 型フラッシュ・メモリの構造 ● メモリ・セルの構造 8192バイト×8ビット=65536ビット (1ページ当たりのトランジスタ・セル数) ト 冗長 領域 1024 バイト 8192バイト 1024 バイト ト 8192バイト ページ1 8ビ ッ ページ0 8ビ ッ データ領域 NAND 型フラッシュ・メモリの構造を図 1 に示し ます. メモリ・セル・アレイが,行デコーダと列デコーダ ⋮ ページ2 ブロック0 (8Kバイト×128ページ =1Mバイト) ⋮⋮⋮⋮⋮⋮ ブロック1 ⋮ ページ127 ページ0 ページ127 ブロックN 図 2 メモリ・セル・アレイのブロック構造 2xnm プロセス,SLC(Single Level Cell) 44 ページ: プログラム/ 読み出し単位 ブロック: 消去単位 で管理され,そこに昇圧回路が接続されています. メモリ・セル・アレイは,図 2 に示すようなメモ リ・ブロック構造になっています. 1 ページ= 8192 + 1024 というのは,1 ページ当たり, データ領域が 8192 バイト(8K バイト) ,冗長領域が 1024 バイト(1K バイト)という意味です.冗長領域は, データ領域の管理用のエリアであり,例えば ECC 用 のパリティなどが格納されています. ここで重要なのは,データ領域が 8K バイト,つま り 65536 ト ラ ン ジ ス タ・ セ ル(8192 × 8 ビ ッ ト )が 1 ページに直列で接続されていることです. 一つのトランジスタ・セルの構造を図 3 に示します. 上から,制御ゲート(CG) ,酸化膜,フローティング・ 2015 年 2 月号

© Copyright 2026