E級増幅器を用いたEER送信機におけるMOSFETの非線形

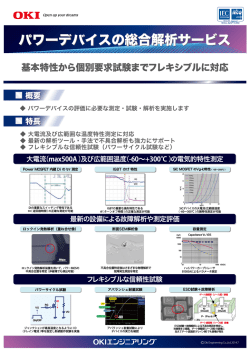

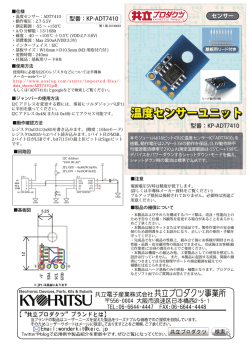

社団法人 電子情報通信学会 THE INSTITUTE OF ELECTRONICS, INFORMATION AND COMMUNICATION ENGINEERS 信学技報 TECHNICAL REPORT OF IEICE. E 級増幅器を用いた EER 送信機における MOSFET の非線形容量の影響 魏秀欽† 永島和治†† 関屋大雄†† 末次正† † 福岡大学工学部電子情報工学科 〒 814-0180 福岡市城南区七隈 8-19-1 †† 千葉大学大学院融合科学研究科 〒 263–8522 千葉市稲毛区弥生町 1–33 E-mail: †[email protected], ††[email protected] あらまし 本稿では E 級増幅器に包絡線除去・再生 (Envelope Elimination and Restoration:EER) 技術を用いた送信 機における, MOSFET の寄生容量が出力の包絡線に与える影響を解析的に表現する. 本稿では, ドレイン-ソース間の 非線形寄生容量およびゲート-ドレイン間の線形寄生容量を考慮する. 解析結果および実験結果より, MOSFET の非線 形容量の影響で出力電圧の包絡線は供給電圧に対して非線形特性を呈することが示される. さらに, 入力電圧波形によ り出力電圧および入力電圧と出力電圧の位相差に影響を与えることを示す. キーワード EER 送信機, E 級増幅器, 寄生容量, 非線形性 MOSFET Nonlinear Capacitance Effect on EER Transmitter with Class-E Amplifier Xiuqin WEI† , Tomoharu NAGASHIAMA†† , Hiroo SEKIYA†† , and Tadashi SUETSUGU† † Dept of Electronics Engineering and Computer Science, Fukuoka University 8-19-1, Nanakuma, Johnan, Fukuoka, 814-0180 Japan †† Graduate School of Advanced Integration Science, Chiba University 1-33, Yayoi-cho, Inage-ku, Chiba-shi, Chiba, 263–8522 Japan E-mail: †[email protected], ††[email protected] Abstract This paper presents analytical expressions of the MOSFET-parasitic-capacitance effects on the output envelope of the EER transmitter, taking into account the MOSFET linear gate-to-drain and nonlinear drain-to– source parasitic capacitances in the class-E amplifier. The analysis is useful to predict the behavior of the EER transmitter using the class-E amplifier. It is shown that the envelope of the output voltage is not in proportion to the dc-supply voltage due to the MOSFET-parasitic-capacitance effects. Additionally, the driving voltage waveform affects the output-voltage amplitude and phase shift between the driving voltage and the output voltage. Key words EER transmitter, class-E amplifier, parasitic capacitance, nonlinearity 1. は じ め に め, スイッチング増幅器の線形化に非常に適している. E 級増幅器は素子が理想的に線形動作すると, 供給電圧に対 E 級増幅器 [1]- [12] は次世代の無線通信用電力増幅器の有力 し出力電圧が比例するという特徴を持つ [3]- [5]. しかしながら, 候補として研究開発が進められている. A, B, C 級増幅器など 高周波数で動作する場合, シャントキャパシタの中で MOSFET 非スイッチング増幅器は特に高バックオフ領域において大きな の寄生容量の割合が支配的になる. ここで MOSFET のドレイ 損失が発生する. それに対し D, E 級増幅器などスイッチング ン-ソース間の寄生容量は非線形特性を持つため [6]- [9], その結 増幅器は電力変換効率を大幅に改善することができ, ひいては 果供給電圧と出力の振幅の線形性が失われる. さらに, ゲート- 電池の長寿命化につながる. スイッチング増幅器は非線形増幅 ドレイン間の寄生容量の影響で, 入力電圧の波形により, 出力電 器であり, 増幅器の出力において振幅と位相を変調させるため 圧が影響を受けることも報告されている [10]. しかし, これまで にいくつかの手法が提案されている [1], [2]. その一つが包絡線 寄生容量の非線形性が出力の振幅に与える影響についての検討 除去・再生 (Envelope Elimination and Restration:EER) であ はほとんど行われていなかった. E 級増幅器を EER 送信機に る. EER は増幅器の出力段に電力合成回路を必要としないた 適用する場合, この特性をあらかじめ解析的に把握しておくこ —1— Envelope detector A(t) Video power dc supply (modulated) conditioner PRF = H(VDD ) L LRFC I DD VDD Shunt Capacitance S Limiter vg Sin (t) Class-E power amplifier C Lr jX DS vg vs Cds CS io vo Cext R Sout (t) (a) 図 1 E 級増幅器を用いた EER 送信機 IDD とは, プレディスト―ション技術などで対応するためにも重要 VDD である. 本稿では E 級増幅器に包絡線除去・再生 (Envelope Elimi- iCgd iMOS Cgd v is Cgd S vg L LRFC C L jX io iCds DS vo R Cds vs nation and Restoration:EER) 技術を用いた送信機における, (b) び実験結果より, MOSFET の非線形容量の影響で出力電圧の 包絡線は供給電圧に対して非線形特性を呈することが示される. さらに, 入力電圧波形により出力電圧および入力電圧と出力電 圧の位相差に影響を与えることを示す. 解析による予測と実験 結果は非常によく一致しており, 解析の妥当性が示される. 2. E 級増幅器を用いた EER 送信機 図 1 に E 級増幅器を用いた EER 送信機のシステム構成を示 す [1], [2]. ここで原信号 Sin (t) は振幅と位相情報を含んでい る. このふたつの信号は分離され, 位相信号はリミッタを用い ることで定振幅の入力信号 vg に変換され, E 級増幅器への入力 となる. 一方, 振幅情報, つまり搬送波より十分低い周波数から なる包絡線信号は A(t) へと変換され, E 級増幅器の供給電圧 ON OFF Vth Switch voltage vS びゲート-ドレイン間の線形寄生容量を考慮する. 解析結果およ Output voltage vo 表現する. 本稿では, ドレイン-ソース間の非線形寄生容量およ Driving signal v MOSFET の寄生容量が出力の包絡線に与える影響を解析的に 0 ZVS/ZDVS 0 0 (c) 図 2 E 級増幅器. (a) 回路構成. (b) 解析に用いた等価回路. (c) 最適 波形の例. となる. この状態で E 級増幅器を動作させると, 出力信号 Sout において, 位相情報と振幅情報が再生された増幅器信号を得る ことができる. 図 2(a) に E 級増幅器の回路構成を示す. EER 送信機では, A(t) の周波数は搬送波周波数, つまり入力信号 vg の周波数よ り十分低いため, 増幅器の 1 周期動作においては直流入力 VDD としてモデル化される. 図 2(c) に増幅器 1 周期分の最適動作波 形を示す. 本稿では, MOSFET を駆動する入力信号 vg を, vg (θ) = −Vg sinθ + Vth (1) とモデル化する. ここで, Vg は入力電圧の振幅, Vth は MOS- FET のスレッショルド電圧を表す. つまり本稿では 0 < θ < =π < で MOSFET がオフ状態, π < θ = 2π で MOSFET がオン状 態であることを仮定する. スイッチがオフの間, 入力インダク タと共振フィルタを流れる電流の差がシャントキャパシタ CS に流れ, スイッチ電圧 vS が生じる. もしすべての受動素子が線 形動作すれば, 出力電圧の振幅と供給電圧の比は供給電圧に対 し一定であり, 他の電圧, 電流も振幅は変わるが波形は変化し がって, E 級増幅器に EER 線形化技術を適用することにより 高効率な線形送信機を設計できる. しかし, シャントキャパシタ CS は周波数が高くなるほどそ の値が小さくなり, シャントキャパシタに占める MOSFET の 寄生容量の割合が大きくなる. 本稿ではシャントキャパシタ は MOSFET の寄生容量のみからなる場合について考察する. MOSFET のドレイン-ソース間の寄生容量はドレイン-ソース 間電圧 vS に対し Cj0 Cds = q vS , 1+ Vbi (2) で表される非線形特性を有する [6]- [9]. ここで, Vbi は内蔵電位, Cj0 は vS =0 のときの容量値である. さらに MOSFET のゲー ト-ドレイン間の寄生容量がスイッチ電圧の波形に影響を及ぼす ことも知られている [10]- [12]. これらの影響により, 供給電圧 と出力電圧の振幅の線形性が崩れることが予想されるが, その 定性的, 定量的評価は行われていない. ない. この場合, オンに切り替わる瞬間にスイッチ電圧は零ま たその傾きも零となる E 級スイッチングを常に達成する. した —2— 3. MOFSET の寄生容量考慮した E 級増幅器 の解析 for 0 < θ < = 2πD (8) と表現される. ここで, iCgd , iCds はそれぞれ MOSFET の寄生 容量 Cgd , Cds を流れる電流である. (8) および vS (0) = 0 から, 3. 1 解析の仮定 1. 図 2(b) のように, MOSFET はスイッチ素子, ドレイン- vS ω 0 ソース間容量, ゲート-ドレイン間容量, 逆並列ダイオードでモ Z デル化される. 2. シャントキャパシタは (2) で表されるドレイン-ソース間 Z 本稿の解析は下記の仮定に基づいている. Cgd + r Cj0 dvS 0 + 0 vS 1+ θ Z sinθ ωCgd Vg d(sinθ)0 0 Vbi iM OS dθ0 = (9) 0 寄生容量のみで構成される. 3. ゲート-ドレイン間の寄生容量は線形動作する [10]- [12]. が得られる. さらに, (5), (9) より, 4. MOSFET と逆並列ダイオードは理想スイッチとして動 vS (θ) = 2gVbi g + h(θ) − h 作する. スイッチの時比率は (1) により D = 0.5 である. 逆並 列ダイオードは MOSFET がオフのとき, スイッチ電圧が零に なったときオンに切り替わる. g 2 + 2gh(θ) + 1 (10) を得る. ここで, IDD θ + Im [cos (θ + ϕ) − cosϕ] − ωCgd Vg sinθ +1,(11) 2ωCj0 Vbi h(θ) = 5. 入力電圧は図 2(b) のように理想電圧源とする. i p 6. 共振フィルタの Q 値は十分高く, 出力電流は正弦波と なる. g= 7. 入力インダクタは十分高く供給電流は直流 IDD となる. 8. MOSFET の寄生容量を含むすべての受動素子の寄生抵 抗は無視する. Cj0 Cgd (12) である. 仮定 7 より, 供給電圧とスイッチ電圧の平均値の間に 3. 2 回 路 解 析 VDD = 仮定 6 より, 増幅器の出力電流と電圧はそれぞれ io (θ) = Im sin(θ + ϕ), (3) vo (θ) = RIm sin(θ + ϕ) = Vm sin(θ + ϕ) (4) 1 2π Z 2π vS (θ)dθ の関係が成立する. (13) を変形すると, 1 = と表現される. ここで Im , Vm はそれぞれ出力電流, 出力電圧 g Vbi π VDD D A 2 2πD (cos2πD − 1)} − 送信機の中で, この位相差は情報を持っており, 固定される必要 n RIDD Vm + VDD VDD 1 Vg [sin(2πD + ϕ) −sinϕ − 2πDcosϕ] + gA Vbi 2πD(g + 1) + Z の振幅であり, ϕ は入力電圧と出力電圧の位相差である. EER n 2π 2 D2 (g + 1)2 + gA 0 がある. Vm Vg +gA [cos(θ + ϕ) −cosϕ] − sinθ VDD Vbi 仮定 6, 7 より, MOSFET 素子を流れる電流は iM OS (θ) = IDD − Im sin(θ + ϕ) (5) となる. 0 < θ < = 2πD において, スイッチはオフ状態である. したがって, スイッチに流れる電流は iS (θ) = 0 (13) 0 for 0 < θ < = 2πD (6) (7) でフーリエ解析すると Vm 1 = π Z XIm = 2π vS (θ)sin(θ + ϕ)dθ, (15) 0 1 π Z 2π vS (θ)cos(θ + ϕ)dθ (16) 0 と表せる. (15) および (16) を正規化すると, それぞれ 子に流れる電流は iM OS (θ) = iCgd (θ) + iCds (θ) + iS (θ) dθ (14) インピーダンスを Z = R + jX とする. このとき, 動作周波数 と表され, したがって, スイッチがオフ状態のとき MOSFET 素 = ωCgd À o0.5 が導出される. 動作周波数における共振フィルタ L − C − R の となる. (1) より, ゲート-ドレイン間の寄生容量にかかる電圧は vCgd = vS − vg = vS + Vg sinθ − Vth RIDD θ VDD dvCgd dvS Cj0 + ωr dθ vS dθ 1+ Vbi Cj0 dvS + ωCgd Vg dsinθ = ω Cgd + r dθ vS dθ 1+ Vbi Vm 2g Vbi = h(g + 1)[cosϕ − cos(2πD + ϕ)] VDD π VDD n A RIDD + − [2πDcos(2πD + ϕ) − sin(2πD + ϕ) + sinϕ] 2 VDD h 1 Vm 1 cos2ϕ − cos2(2πD + ϕ) + VDD 4 4 +cosϕcos(2πD + ϕ) − cos2 ϕ 1 Vg + 2gA Vbi h ¤ 1 1 sin(4πD + ϕ) − sinϕ − 2πDcosϕ 2 2 i¾ —3— 表 1 IRF510 MOSFET のパラメータ 2πD 0 図3 vS vS Body-diode on duration θ 2π π (a) Vbi 2πD' 0 Vth Cj0 Cgd 0.8 V 3.70 V 366.5 pF 40.1 pF θ 2π π (b) 表 2 回路素子値 Theoretical Measured Difference ∗ スイッチ電圧の波形例. (a) スイッチの瞬間にジャンプが生じる LRF C 110 µH 115 µH 波形例. (b) スイッチがオンに切り替わる前に零に達する波形例. C 83.4 pF 84.0 pF 0.72 % L 21.8 µH 21.6 µH −0.92 % R 54.7 Ω 55.0 Ω Z 2πD − n 0 RIDD Vm (g + 1) + gA θ + gA [cos(θ + ϕ) VDD VDD À o0.5 sin(θ + ϕ)dθ , (17) h 1 Vg 2gA Vbi Z 2πD − i¾ 1 1 cosϕ − cos(4πD + ϕ) − 2πDsinϕ 2 2 n (g + 1)2 + gA 0 −cosϕ] − 仕様として与えられる. したがって, RIDD /VDD , Vm /VDD , ϕ のみが未知変数となる. これらの未知変数は (14), (17), (18) を 連立方程式として解くことにより導出される. 本稿では, 連立 XIm 2g Vbi = h(g + 1)[sin(2πD + ϕ) − sinϕ] VDD π VDD n A RIDD + [2πDsin(2πD + ϕ) + sin(2πD + ϕ) − cosϕ] 2 VDD h Vm 1 1 + cos2(2πD + ϕ) − sin2ϕ + πD VDD 4 4 −cosϕsin(2πD + ϕ) + cosϕsinϕ] − 0.55 % 2 Vg sinθ Vbi −cosϕ] − 4.55 % Vg sinθ Vbi o0.5 法を用いて近似する. 4. 考 察 本章では, 前章にて導出した解析から得られる結果から, MOSFET の寄生容量および入力電圧が出力の包絡線, 位相差 にあたえる影響について考察する. まず, E 級動作条件を満足す る E 級増幅器の設計を行う. 設計仕様として, 供給電圧 VDD = RIDD Vm θ + gA [cos(θ + ϕ) VDD VDD À cos(θ + ϕ)dθ 代数方程式は Newton 法を用い解き, さらに式中の積分は台形 15 V, 入力周波数 f = 4 MHz, MOSFET の時比率 D = 0.5, 入力電圧の振幅 Vg = 6 V, 共振フィルタの Q 値 Q = 10 を与 える. また, 実験では IRF510 MOSFET をスイッチング素子と (18) して用いる. 表 1 に IRF510 MOSFET の主要パラメータを示 す. これらのパラメータは PSpice の素子モデルから抽出したも と書き直すことができる. のである. これらのパラメータおよび設計仕様より, VDD /Vbi 寄生容量の非線形性を考慮しているため, 供給電圧が設計仕 様値から変化した時, スイッチ波形は E 級動作条件を満足しな い. EER システムでは, 2 種類のスイッチングパターンを考慮 する必要がある. 一つは, スイッチ電圧がオンになるまで常に 正値を取り, スイッチングの瞬間にジャンプを起こす図 3(a) の 状態. もうひとつはスイッチがオンになる前に電圧が零に達し, 逆並列ダイオードがオンになる図 3(b) の状態である. 図 3(a) の状態においては, (14), (17), (18) 式をそのまま用いることが できる. 一方, 図 3(b) の状態においては, 逆並列ダイオードが 動作するため, 仮定 4 よりスイッチがオンになる時間が延びる ことと等価となる. これを解析式に反映させるためには, 時比 率 D を「スイッチ電圧が正である時比率」に置き換えればよ い. したがって, 時比率は ( D= 0.5 D if 0 if vS (θ = π) > =0 vS (θ = π) < 0 g + h(2πD0 ) − g 2 + 2gh(2πD0 ) + 1 = 0 て文献 [10] に示される設計手順に従って計算すると, 表 2 に与 えられる素子値を導出することができる. 本稿では最適状態か ら供給電圧 VDD および入力電圧の振幅 Vg を変化させたとき の, E 級増幅器の特性について考察する. 図 4 に VDD /Vbi に対する正規化された出力電圧の振幅およ び位相差の特性を示す. また, 図中 Vg /Vbi = 0 は入力電圧が矩 形波であることと等価であり, Vg /Vbi = 7.5 は正弦波 (設計仕 様) であることを示している. EER システムは増幅器の供給電圧に対して出力電圧の振幅 が比例することを前提に設計されている. 実際, シャントキャパ シタが線形特性を有するとき, Vm /VDD は VDD に依存せず一 定である [4], [5]. しかし, 図 4(a) より Vm /VDD は VDD /Vbi に 対して変動することを示している. これは, Vm と VDD の間に (19) 非線形性が生じていることを意味している. つまり, MOSFET の寄生容量の非線形により, EER 送信機の出力包絡線に歪が生 と表すことができ, D0 は p = 18.75, Vg /Vbi = 7.5, g = 9.14 を得る. これらの仕様を用い じる. さらに, 入力電圧を矩形波にすると, その歪率が正弦波入 (20) 力と比較して高くなることが分かる. この結果は, 入力電圧の 振幅を小さくことにより歪率を低減できることを示唆している. より数値的に導出できる. 上 述 し た す べ て の 解 析 式 か ら, E 級 増 幅 器 の 特 性 は 一方で, 入力電圧の振幅を小さくすると, 入力信号の SN 比が小 さくなるため, その回路実装は難しくなる. 加えて入力電圧の RIDD /VDD , Vm /VDD , ϕ, VDD /Vbi , Vg /Vbi , g, X, ωCj0 R の 振幅を抑えるとスイッチ速度が遅くなり, 電力変換効率の劣化 関数で表されることが分かる. 一般的に, VDD /Vbi , Vg /Vbi , g, につながる. つまり, 歪率の低減と回路実装の困難性, および高 X, ωCj0 R は EER 送信機を設計する立場から回路パラメータ, —4— 効率化にはトレードオフの関係があることが分かる. 1.1 図 4(b) より, VDD /Vbi の変動に対し位相差も一定値となら ないことが分かる. 理想的には, 2 章で述べた通り入力信号の 位相は情報を含むため, 入力電圧と出力電圧の位相差は常に一 Vm/VDD 定であることが望まれる. この結果は MOSFET の寄生容量は EER 送信機の振幅情報だけでなく, 位相情報にも歪を生じさせ ることを示している. さらに, 入力電圧の波形により位相差の Nominal condition 1 変動範囲が異なることが分かる. 図 4(a), (b) から, 入力電圧を Vg/Vbi = 7.5, Theoretical Vg/Vbi = 0.0, Theoretical Vg/Vbi = 7.5, Experimental Vg/Vbi = 0.0, Experimental 生成する駆動回路の設計は重要であり, 出力の歪特性は入力電 圧に依存することが分かる. MOSFET の寄生容量に起因するこれら非線形性は本稿で示 0.9 0 された解析式より予測することができる. したがって, 本稿で指 10 20 30 VDD/Vbi (a) 摘した歪に関する問題に対して改善手法を適用することができ -0.4 る. その一つがプレディスト―ションであり, 予測される歪率の 逆関数をあらかじめ入力に乗算することにより EER 送信出力 の歪率を低減させることができる. また, 図 4 より, VDD /Vbi が Nominal condition 大きくなるにつれ, 変動の幅が限られることが分かる. VDD /Vbi ϕ (rad) が大きいほどスイッチ電圧は高くなる. 一方, (2) から, スイッ チ電圧が高くなるほど寄生容量の変動が小さくなることが分か -0.8 る. つまり, VDD /Vbi が大きいほど, ドレイン-ソース間の寄生 Vg/Vbi = 7.5, Theoretical Vg/Vbi = 0.0, Theoretical Vg/Vbi = 7.5, Experimental Vg/Vbi = 0.0, Experimental 容量における非線形性の影響が小さくなるためである. 図 4 における, 解析による理論値と実験値は定量的によく一 致しており, 本稿で示した解析の妥当性が示される. -1.2 0 5. む す び 20 30 VDD/Vbi (b) 本稿では E 級増幅器に包絡線除去・再生 (Envelope Elimi- nation and Restoration:EER) 技術を用いた送信機における, 10 図4 VDD /Vbi に対する諸特性. (a) 正規化出力振幅 Vm /VDD . (b) 位相差 ϕ. MOSFET の寄生容量が出力の包絡線に与える影響を解析的に 表現した. 解析結果および実験結果より, MOSFET の非線形容 量の影響で出力電圧の包絡線は供給電圧に対して非線形特性を 呈することが確認され, 解析結果よりその定量的予測が可能で あることを示した. さらに, 入力電圧波形により出力電圧および [8] 入力電圧と出力電圧の位相差に影響を与えることを示し, その 上で歪率の低減とシステムの高電力変換効率化の間にはトレー ドオフの関係があることを示した. 解析による理論結果は実験 [9] 結果は非常によく一致しており, 解析の妥当性が示された. 文 献 [1] S. C. Cripps, RF Power Amplifiers for Wireless Communications. Norwood, MA: Artech House, 2006. [2] P. Reynaert and M. Steyaert, RF Power Amplifiers for Mobile Communications. Netherlands: Springer, 2006. [3] N. O. Sokal and A. D. Sokal, “Class E—A new class of high-efficiency tuned single-ended switching power amplifiers,” IEEE J. Solid-State Circuits, vol. SC-10, no. 3, pp. 168–176, Jun. 1975. [4] F. H. Raab, “Effects of circuit variations on the class-E tuned power amplifier,” IEEE J. Solid-State Circuits, vol. SC-13, no. 2, pp. 239–247, Apr. 1978. [5] M. K. Kazimierczuk, RF Power Amplifiers. New York, NY: John Wiley & Sons, 2008. [6] M. J. Chudobiak, “The use of parasitic nonlinear capacitors in class-E amplifiers,” IEEE Trans. Circuits Syst. I, vol. 41, no. 12, pp. 941–944, Dec. 1994. [7] T. Suetsugu and M. K. Kazimierczuk, “Analysis and de- [10] [11] [12] sign of class E amplifier with shunt capacitance composed of nonlinear and linear shunt capacitances,” IEEE Trans. Circuits Syst. I, vol. 51, no.7, pp. 1261–1268, Jul. 2004. T. Suetsugu and K. M. kazmierczuk, “Output characteristics of class E amplifier with nonlinear shunt capacitance versus supply voltage, ” in Proc. IEE ISCAS, New Orleans, LA, May 2007, pp. 541–544 A. Mediano, P. M. Gaudo, and C. K. Bernal, “Design of class E amplifier with nonlinear and linear shunt capacitances for any duty cycle,” IEEE Trans. Microw. Theory Tech., vol. 55, no. 3, pp. 484–492, Mar. 2007. X. Wei, H. Sekiya, S. Kuroiwa, T. Suetsugu, and M. K. Kazimierczuk, “Design of class-E amplifier with MOSFET linear gate-to-drain and nonlinear drain-to-source capacitances,” IEEE Trans. Circuits Syst. I, vol. 58, no.10, pp. 2556–2565, Oct. 2011. D. K. Choi and S. I. Long, “The effect of transistor feedback capacitance in class-E power amplifiers,” IEEE Trans. Circuits Syst. I, vol. 50, no. 12, pp. 1556–1559, Dec. 2003. D. K. Choi and S. I. Long, “A physically based analytic model of FET class E power amplifiers-designing for maximum PAE,” IEEE Trans. Microw. Theory Tech., vol. 47, no. 9, pp. 1712–1720, Sep. 1999. —5—

© Copyright 2026