超低オフセット電圧の デュアル・オペアンプ - Analog Devices, Inc.

超低オフセット電圧の デュアル・オペアンプ AD708 特長 ピン配置 非常に高い DC 精度 OUTPUT A 1 最大電圧ノイズ: 0.35 μV p-p (0.1 Hz~10 Hz) –IN A 2 最小オープン・ループ・ゲイン: 5 mV/V +IN A 3 –VS 4 最小 CMRR: 130 dB 最小 PSRR: 120 dB AD708 – + A – B + TOP VIEW (Not to Scale) マッチング特性 最大オフセット電圧マッチング: 30 μV 8 +VS 7 OUTPUT B 6 –IN B 5 +IN B 05789-001 最大オフセット電圧: 30 μV 最大オフセット電圧ドリフト: 0.3 μV/°C 図1.PDIP (N)および CERDIP (Q)パッケージ 最大オフセット電圧ドリフト・マッチング: 0.3 μV/°C 最小 CMRR マッチング: 130 dB 8 ピンのナロー・ボディ PDIP または ハーメチック CERDIP、またはハーメチック CERDIP/883B パッケ ージを採用 概要 AD708 は高精度のデュアル・モノリシック・オペアンプです。各 アンプは、いずれのバイポーラ・オペアンプでも最大オフセット 電圧と最大オフセット電圧ドリフトで、優れた DC 精度を提供し ます。 マッチング仕様はデュアル・オペアンプの中でも最も優れたもの です。さらに、AD708 は 5 V/μV の最小オープン・ループ・ゲイ ンを提供し、350 nV p-p (0.1 Hz~10 Hz)の最大入力電圧ノイズを 保証しています。すべての DC 仕様は、温度に対する優れた安定 性を示し、オフセット電圧ドリフトは 0.1 μV/°C (typ)で、入力バ イアス電流ドリフトは最大 25 pA/°C です。 AD708 には 4 種類の性能グレードがあります。AD708J は 0°C~ 70°C の商用温度範囲仕様で、ナロー・ボディ PDIP を採用してい ます。AD708A と AD708B は−40°C~+85°C の工業用温度範囲仕様 で、CERDIP パッケージを採用しています。 Rev. C AD708S は−55°C~+125°C の軍用温度範囲仕様で、MIL-STD-883B に準拠した CERDIP 軍用バージョン・パッケージを採用していま す。 製品のハイライト 1. AD708 は優れたマッチングと個別仕様の組み合わせを持つた め、高ゲイン高精度の計装アンプの構築に最適です。 2. AD708 は低オフセット電圧ドリフトかつ低ノイズであるため、 システム全体性能を犠牲にすることなく非常に小さい信号を 増幅することができます。 3. AD708 は、10 V/µV (typ)のオープン・ループ・ゲインと 140 dB 同相モード除去比を持つため、高精度アプリケーション に最適です。 アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に 関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、 アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様 は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。 ※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2006 Analog Devices, Inc. All rights reserved. 社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03(5402)8200 大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06(6350)6868 本 AD708 目次 特長......................................................................................................... 1 動作原理 ............................................................................................... 10 ピン配置................................................................................................. 1 クロストーク性能 ........................................................................... 10 概要......................................................................................................... 1 ゲイン= −100 での動作 ................................................................... 11 製品のハイライト ................................................................................. 1 高精度可変ゲイン・アンプ............................................................ 11 改訂履歴................................................................................................. 2 ブリッジ・シグナル・コンディショナ........................................ 12 仕様......................................................................................................... 3 高精度絶対値回路 ........................................................................... 12 絶対最大定格 ......................................................................................... 5 ESDに関する注意.............................................................................. 5 代表的な性能特性 ................................................................................. 6 マッチング特性 ................................................................................. 9 改訂履歴 1/06—Rev. B to Rev. C Updated Format...................................................................... Universal Removed TO-99 Package ....................................................... Universal Deleted AD707 References .................................................... Universal Deleted LT1002 Reference...................................................................1 Deleted Figure 1 ...................................................................................1 Deleted Metalization Photograph .........................................................5 Moved Figure 25, Figure 26, and Figure 27 to Theory of Operation section ...........................................................10 Updated Outline Dimensions..............................................................13 Changes to Ordering Guide ................................................................13 2/91—Rev. A to Rev. B Rev. C - 2/13 - 受動部品の選択 ............................................................................... 12 外形寸法 ............................................................................................... 13 オーダー・ガイド ........................................................................... 13 AD708 仕様 特に指定がない限り、25°C、±15 V dc。 表1. Parameter Conditions AD708J/AD708A Min1 Typ Max1 INPUT OFFSET VOLTAGE2 TMIN to TMAX Drift Long Term Stability INPUT BIAS CURRENT TMIN to TMAX Average Drift OFFSET CURRENT VCM = 0 V TMIN to TMAX Average Drift 5 15 0.1 0.3 30 50 0.3 μV μV μV/°C μV/month 1.0 2.0 15 2.5 4.0 40 0.5 1.0 10 1.0 2.0 25 0.5 1.0 10 1 4 30 nA nA pA/°C 0.5 2.0 2 2.0 4.0 60 0.1 0.2 1 1.0 1.5 25 0.1 0.2 1 1 1.5 25 nA nA pA/°C 30 50 0.3 1.0 2.0 μV μV μV/°C nA nA dB dB dB dB dB TMIN to TMAX TMIN to TMAX Channel Separation Unit 50 65 0.4 Offset Voltage Drift Input Bias Current Power Supply Rejection AD708S Typ Max1 5 15 0.1 0.3 50 75 0.4 1.0 2.0 80 150 1.0 4.0 5.0 120 110 110 110 135 Min1 100 150 1.0 TMIN to TMAX TMIN to TMAX AD708B Typ Max1 30 50 0.3 0.3 MATCHING CHARACTERISTICS3 Offset Voltage Common-Mode Rejection Min1 140 130 130 120 120 140 140 130 130 120 120 140 140 INPUT VOLTAGE NOISE 0.1 Hz to 10 Hz f = 10 Hz f = 100 Hz f = 1 kHz 0.23 10.3 10.0 9.6 0.6 18 13.0 11.0 0.23 10.3 10.0 9.6 0.6 12 11.0 11.0 0.23 10.3 10.0 9.6 0.35 12 11 11 μV p-p nV/√Hz nV/√Hz nV/√Hz INPUT CURRENT NOISE 0.1 Hz to 10 Hz f = 10 Hz f = 100 Hz f = 1 kHz 14 0.32 0.14 0.12 35 0.9 0.27 0.18 14 0.32 0.14 0.12 35 0.8 0.23 0.17 14 0.32 0.14 0.12 35 0.8 0.23 0.17 pA p-p pA/√Hz pA/√Hz pA/√Hz COMMON-MODE REJECTION RATIO VCM = ±13 V 120 140 130 140 130 140 dB TMIN to TMAX 120 140 130 140 130 140 dB VO = ±10 V RLOAD ≥ 2 kΩ TMIN to TMAX 3 3 10 10 5 5 10 10 4 4 10 7 V/μV V/μV VS = ±3 V to ±18 V TMIN to TMAX 110 110 130 130 120 120 130 130 120 120 130 130 dB dB 0.5 0.15 0.9 0.3 0.5 0.15 0.9 0.3 0.5 0.15 0.9 0.3 MHz V/μs 200 400 MΩ GΩ OPEN-LOOP GAIN POWER SUPPLY REJECTION RATIO FREQUENCY RESPONSE Closed-Loop Bandwidth Slew Rate INPUT RESISTANCE Differential Common Mode Rev. C 60 200 - 3/13 - 200 400 AD708 Parameter Conditions AD708J/AD708A Min1 Typ Max1 Min1 OUTPUT VOLTAGE RLOAD ≥ 10 kΩ RLOAD ≥ 2 kΩ RLOAD ≥ 1 kΩ TMIN to TMAX 13.5 12.5 12.0 12.0 14 13.0 12.5 13.0 13.5 12.5 12.0 12.0 OPEN-LOOP OUTPUT RESISTANCE POWER SUPPLY Quiescent Current Power Consumption Operating Range 60 4.5 135 12 VS = ±15 V VS = ±3 V ±3 1 AD708B Typ Max1 14.0 13.0 12.5 13.0 Min1 13.5 12.5 12.0 12.0 60 5.5 165 18 ±18 4.5 135 12 ±3 5.5 165 18 ±18 AD708S Typ Max1 ±V ±V ±V ±V 60 Ω 4.5 135 12 ±3 Unit 14 13 12.5 13 5.5 165 18 ±18 mA mW mW V すべての min/max 仕様を保証。太字で示す仕様は、最終電気テストですべての製品ユニットについてテストされます。これらのテスト結果を使って、出荷品質レベル が計算されます。 2 入力オフセット電圧仕様は、TA = 25°C で 5 分間動作後について保証します。 3 マッチングは、2 個のアンプのパラメータ間の差として定義されます。 Rev. C - 4/13 - AD708 絶対最大定格 上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久 的な損傷を与えることがあります。この規定はストレス定格の規 定のみを目的とするものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼 性に影響を与えます。 表2. Parameter Rating Supply Voltage Internal Power Dissipation1 Input Voltage2 Output Short-Circuit Duration Differential Input Voltage Storage Temperature Range (Q) Storage Temperature Range (N) Lead Temperature (Soldering 60 sec) ±22 V ±VS Indefinite +VS and −VS −65°C to +150°C −65°C to +125°C 300°C 熱特性。 8 ピン PDIP: θJC = 33°C/W, θJA = 100°C/W 8 ピン CERDIP: θJC = 30°C/W, θJA = 110°C/W 2 ±22 V より低い電源電圧の場合、最大入力電圧は電源電圧に等しくなりま す。 1 ESDに関する注意 ESD(静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することが あります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被 った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を 講じることをお勧めします。 Rev. C - 5/13 - AD708 代表的な性能特性 特に指定がない限り、VS = ±15 V、TA = 25°C。 8 –0.5 7 +V SUPPLY CURRENT (mA) –1.0 –1.5 1.5 1.0 6 5 4 3 2 –V –VS 1 0 5 10 15 20 0 25 05789-005 0.5 05789-002 COMMON-MODE VOLTAGE LIMIT (V) (REFERRED TO SUPPLY VOLTAGES) +VS 0 3 6 SUPPLY VOLTAGE (±V) 図2.電源電圧対同相モード入力範囲 100 15 18 21 24 0.2 0.3 0.4 256 UNITS TESTED –55°C TO +125°C 90 +VOUT 80 NUMBER OF UNITS –1.0 –1.5 RL = 10kΩ RL = 2kΩ 1.5 1.0 60 50 40 30 0 5 10 15 20 05789-006 –VS 70 20 –VOUT 0.5 05789-003 OUTPUT VOLTAGE SWING (±V) (REFERRED TO SUPPLY VOLTAGES) 12 図5.電源電圧対電源電流 +VS –0.5 9 SUPPLY VOLTAGE (±V) 10 0 –0.4 25 –0.3 –0.2 SUPPLY VOLTAGE (±V) –0.1 0 0.1 OFFSET VOLTAGE DRIFT (µV/°C) 図3.電源電圧対出力電圧振幅 図6.オフセット電圧ドリフトの分布 35 100 IO = 1mA 10 OUTPUT IMPEDANCE (Ω) 25 20 ±15V SUPPLIES 15 10 05789-004 100 1k 0.1 0.01 0.0001 0.1 10k LOAD RESISTANCE (Ω) 1 10 100 1k 10k FREQUENCY (Hz) 図4.負荷抵抗対出力電圧振幅 Rev. C AV = +1 0.001 5 0 10 AV = +1000 1 05789-007 OUTPUT VOLTAGE (V p-p) 30 図7.出力インピーダンスの周波数特性 - 6/13 - 100k 16 35 14 30 12 OPEN-LOOP GAIN (V/µV) 40 20 15 10 5 8 VOUT = ±10V 6 4 0 1 10 RL = 10kΩ RL = 2kΩ 2 0 –60 100 –40 –20 0 DIFFERENTIAL VOLTAGE (±V) 45 16 40 14 35 30 25 1/F CORNER 0.7Hz 15 1 80 100 120 140 RLOAD = 2kΩ 10 8 6 4 10 0 100 05789-012 2 05789-009 5 0.1 60 12 10 0 40 図11.オープン・ループ・ゲインの温度特性 OPEN-LOOP GAIN (V/µV) INPUT VOLTAGE NOISE (nV/ Hz) 図8. 差動入力電圧対入力バイアス電流 20 20 TEMPERATURE (°C) 0 5 10 FREQUENCY (Hz) 15 20 25 SUPPLY VOLTAGE (V) 図9.入力ノイズ・スペクトル密度 図12.電源電圧対オープン・ループ・ゲイン 140 RL = 2kΩ CL = 1000pF 1s OPEN-LOOP GAIN (dB) VOLTAGE NOISE (100nV/DIV) 120 100 0 30 60 80 90 PHASE MARGIN = 43° 60 120 40 150 GAIN 20 180 –20 05789-013 05789-010 0 TIME (1s/DIV) 0.01 0.1 1 10 100 1k 10k 100k 1M 10M FREQUENCY (Hz) 図10.0.1 Hz~10 Hz の電圧ノイズ Rev. C 図13.オープン・ループ・ゲインおよび位相の周波数特性 - 7/13 - PHASE (Degrees) 0 10 05789-011 25 05789-008 INVERTING OR NONINVERTING INPUT BIAS CURRENT (mA) AD708 AD708 160 2mV/DIV 120 100 80 60 40 CH1 0 0.1 05789-014 20 1 10 100 1k 10k 100k 05789-017 COMMON-MODE REJECTION (dB) 140 TIME (2µs/DIV) 1M FREQUENCY (Hz) 図14.同相モード除去比の周波数特性 35 RL = 2kΩ 25°C VS = ±15V FMAX = 2.8kHz 30 OUTPUT VOLTAGE (V p-p) 図17.小信号過渡応答、AV = +1、RL = 2 kΩ、CL = 50 pF 2mV/DIV 25 20 15 10 CH1 0 1k 10k 100k 05789-018 05789-015 5 1M TIME (2µs/DIV) FREQUENCY (Hz) 図18.小信号過渡応答、AV = +1、RL = 2 kΩ、CL = 1000 pF 図15.大信号周波数応答 160 POWER SUPPLY REJECTION (dB) 140 120 100 80 60 40 0 0.001 05789-016 20 0.01 0.1 1 10 100 1k 10k 100k FREQUENCY (Hz) 図16.電源除去比の周波数特性 Rev. C - 8/13 - AD708 マッチング特性 32 16 25°C 14 PERCENTAGE OF UNITS (%) 24 20 16 12 8 0 –50 –40 –30 –20 –10 0 10 20 30 40 10 8 6 4 2 05789-019 4 12 0 –1.0 50 05789-022 PERCENTAGE OF UNITS (%) 28 –0.8 –0.6 OFFSET VOLTAGE MATCH (µV) –0.4 –0.2 0 0.2 0.4 0.6 0.8 1.0 OFFSET CURRENT MATCH (nA) 図19.オフセット電圧マッチングの分布 図22.入力オフセット電流マッチングの分布 32 160 140 24 120 20 16 12 100 80 60 8 40 4 20 0 –0.5 –0.4 –0.3 –0.2 –0.1 0 0.1 0.2 0.3 0.4 0 –60 0.5 05789-023 PSRR MATCH (dB) 28 05789-020 PERCENTAGE OF UNITS (%) –55°C TO +125°C –40 –20 0 OFFSET DRIFT MATCH (µV/°C) 160 14 140 12 120 10 8 6 20 0 0.2 0.4 0.6 0.8 0 –60 1.0 INPUT BIAS CURRENT MATCH (nA) –40 –20 0 20 40 60 80 100 TEMPERATURE (°C) 図21.入力バイアス電流マッチングの分布 Rev. C 120 140 120 140 60 2 –0.2 100 80 40 –0.4 80 100 4 –0.6 60 05789-024 CMRR MATCH (dB) 16 –0.8 40 図23.PSRR マッチングの温度特性 05789-021 PERCENTAGE OF UNITS (%) 図20.オフセット電圧ドリフト・マッチングの分布 0 –1.0 20 TEMPERATURE (°C) 図24.CMRR マッチングの温度特性 - 9/13 - AD708 動作原理 クロストーク性能 図 25、図 26、図 27のように、AD708 は非常に小さいクロストー クを示します。図 25に、AD708 のA側出力を無負荷で−10 Vから +10 Vまでゆっくり(0.2 Hz)動かしたときに、B側に発生するオフ セット電圧を示します。これは、チップ内の消費電力全体が変化 しないためデバイスに対するストレスが最も小さい状態を示して います。出力デバイスの消費電力の位置のみが変化します。図 26 に、A側を 2 kΩ負荷で駆動したときのB側での入力オフセット電 圧変化を示します。この場合チップ内で消費電力が変化し、消費 電力の最大変化は 7.5 Vで発生します。図 27に、最も厳しい条件 でのクロストークを示します。A側は 0 V入力のフォロワとして接 続され、±5 mAのシンク電流およびソース電流が出力されます。 A VIN = ±10V VOUTA 2kΩ 10kΩ B 10Ω VOUTB 10Ω 2V 消費電力のこの大きな変化でも、B 側の入力オフセット電圧は 8 μV (リニア)しか変化しません。 A VIN = ±10V VOUTA ΔVOSB = 1µV/DIV 消費電力= (30 V)(5 mA) = 150 mW B 10Ω 05789-026 10kΩ VOUTB 10Ω VOUTA = 2V/DIV 図26.2 kΩ 負荷でのクロストーク 2V IIN = ±5mA ΔVOSB = 1µV/DIV A 2kΩ VIN = ±10V 10kΩ B 10Ω 05789-025 10Ω VOUTB 2V VOUTA = 2V/DIV 05789-027 ΔVOSB = 2µV/DIV 図25.無負荷時のクロストーク INA = 1mA/DIV 図27.ソースおよびシンク状態でのクロストーク Rev. C - 10/13 - AD708 1/2 ゲイン= −100 での動作 VINA 実際のアプリケーションでのAD708 の優れたDC精度を示すため、 表 3にゲイン= −100 のときの誤差計算値を示します。図 28には、 この構成を示します。 AD708 OUT 1–4 A0 A1 10kΩ 10kΩ 10kΩ S1 S2 表3. 9.9kΩ S3 S4 30 μV/100 mV (100 kΩ)(1 nA)/10 V = 10 ppm Gain (2 kΩ Load) 10 V/(5 × 106)/100 mV = 20 ppm 1kΩ 26.1Ω 26.1Ω 26.1Ω 100Ω –VS 10kΩ 10kΩ AD707 S8 +VS 9.9kΩ S7 = 300 ppm IOS 10kΩ AD7502 S6 S5 OUT 5–8 Noise 0.35 mV/100 mV = 4 ppm VOS Drift (0.3 mV/°C)/100 mV = 3 ppm/°C @ 25°C = 334 ppm > 11 bits −55°C to +125°C = 634 ppm > 10 bits VINB RB 10kΩ 10kΩ 10kΩ 05789-029 Error Sources VOS Maximum Error Contribution AV = 100 (S Grade) (Full Scale: VOUT = 10 V, VIN = 100 mV) RA 1/2 AD708 Total Unadjusted Error With Offset Calibrated Out @ 25°C = 34 ppm > 14 bits −55°C to +125°C = 334 ppm > 11 bits +VS 0.1µF 2 – 1/2 6 AD708 3 + 4 1kΩ 入力ステージでは、AD708S の 30 μV の最大オフセット電圧マッ チングと 1 nA の最大入力バイアス電流マッチングにより非常に高 い DC 精度を実現しています。精度は、AD708 の極めて低いドリ フト性能により温度対して安定に維持されています。 同相モード除去比を最大にするために、 7 0.1µF –VS 1. セレクト・ラインを設定して、ゲイン= 1 かつ VINB =グラウ ンドとなるようにします。 2. 高精度 DC 電圧を VINA に加えて、VO = −VINA が必要な精度に なるように RA を調整します。 3. VINB と VINA を接続し、期待されるフルスケール同相モードに 等しい入力電圧を加えます。 4. VO = 0 V となるように RB を調整します。 VOUT 05789-028 VIN この回路のゲインは、AD7502マルチプレクサのセレクト・ライン A0 とA1 から制御され、1、10、100、1000 が可能です。 0.1%のゲイン精度と高い同相モード除去比を実現するためには、 回路を調整する必要があります。 100kΩ 1kΩ 図29.高精度 PGA 図28.ゲイン-100 の構成 ゲイン誤差を最小にするため、 この誤差計算では抵抗比の誤差がなく、かつ電源変動による誤差 がないものと仮定しています(AD708S の最小 PSRR は 120 dB であ るためこの仮定は現実的です)。外付け抵抗から、不一致と温度ド リフトによりゲイン誤差が発生することがあります。 1. コントロール・ラインを使ってゲイン= 10 を選択し、差動入 力電圧を加えます。 2. 100 Ω のポテンショメータを VO = 10 VIN となるように調整し ます(必要に応じて VIN 振幅を調整します)。 高精度可変ゲイン・アンプ 3. ゲイン= 100 とゲイン= 1000 に対してステップ 1 とステップ 2 を繰り返し、それぞれ 1 kΩ と 10 kΩ のポテンショメータを 調整します。 3 個のオペアンプを使用する可変ゲイン・アンプを 図 29に示しま す。このアンプでは、AD708 の優れたマッチング特性を利用して 高いDC精度を実現しています。 Rev. C - 11/13 - 図 29に示すデザインでは、±1%の抵抗と±5%のポテンショメータ を使う場合、0.1%のゲイン精度と 0.1 μV/Vの同相モード除去比が 可能です。 AD708 ブリッジ・シグナル・コンディショナ 図 30に示す回路でAD708 を使うと、正確で安価なダイナミッ ク・ブリッジ・コンディショナを実現することができます。 AD708 の低オフセット電圧マッチングと低オフセット電圧ドリフ ト・マッチングの組み合わせにより、優れた回路性能を持つ計装 アンプを実現することができます。オープン・ループ・ゲイン、 入力オフセット電流、低入力バイアス電流のようなAD708 の優れ た仕様により、回路精度に制限はありません。 この回路構成では、適切な精度のゲイン抵抗 RG と安定で正確な リファレンス電圧のみが必要です。伝達関数は次式で表されます。 号を正確に処理することができます。さらに、オフセット電圧ド リフトが厳格にマッチングしているため、軍用温度範囲で回路の 分解能を維持することができます。高いDCオープン・ループ・ゲ インと優れたゲイン直線性により、大信号レベルと小信号レベル での回路動作が優れています。 この回路では、大きな DC 誤差は、2 つのアンプのオフセット電 圧、アンプ入力オフセット電流のマッチング、抵抗のミスマッチ ングのみから発生します。AD708S から発生する誤差成分は、 −55°C~+125°C で 0.001%以下です。 25°C での最大誤差は、 30 μV 10 kΩ 1 nA VO = VREF [∆R/(R + ∆R)][RG/R] 10 V AD708S から発生する主な誤差は、次だけです。 +125°C または−55°C での最大誤差は、 VOS_OUT = (VOS_MATCH)(2RG/R) = 30 mV 50 μV 2 nA 10 kΩ VOS_OUT (T) = (VOS_DRIFT)(2RG/R) = 0.3 mV/°C 高精度を実現するためには、抵抗 RG は低ドリフト係数を持つ 0.1%以上である必要があります。 +15V AD580 RG 175kΩ 2.5V VREF R R = 350Ω 10 V 7 ppm @ 125 C 図 32 に、0.05 Hzで±3 mVの入力信号に対するこの回路のVIN 対 VOUTを示します。この回路はゼロ交差で非常に低いオフセットを 持っていることに注意してください。また、この回路は、2 個の ダイオードの極性を逆にすることによりVOUT = −|VIN|を発生する こともできます。 1/2 AD708 R 40 μV/10 μV 4 ppm 1mV 1mV VO R + ΔR 1/2 VOUT = 1mV/DIV AD708 05789-030 887Ω –15V 10kΩ 10kΩ IN459 1 10kΩ 10kΩ 5kΩ VIN = 1mV/DIV IN4591 3.75kΩ VIN 05789-032 図30.ブリッジ・シグナル・コンディショニング回路 1/2 VO = |VIN| AD708 AD708 NOTE 1LOW LEAKAGE DIODES 05789-031 1/2 5kΩ 図31.高精度絶対値回路 高精度絶対値回路 AD708 は、図 31に示す高精度絶対値回路用に最適です。AD708 のオフセット電圧はマッチングしているため、この回路は入力信 Rev. C - 12/13 - 図32.絶対値回路の性能(入力信号= 0.05 Hz) 受動部品の選択 AD708 の高精度と低ドリフト特性をフルに利用するためには、高 品質の受動部品を使ってください。10 ppm/°C 以下の温度係数を 持つディスクリート抵抗や抵抗回路は、Vishay 社、Caddock 社、 Precision Replacement Parts (PRP)社などから提供されています。 AD708 外形寸法 0.400 (10.16) 0.365 (9.27) 0.355 (9.02) 0.005 (0.13) MIN 0.055 (1.40) MAX 8 8 1 5 0.280 (7.11) 0.250 (6.35) 0.240 (6.10) 4 0.310 (7.87) 0.220 (5.59) 0.325 (8.26) 0.310 (7.87) 0.300 (7.62) PIN 1 0.100 (2.54) BSC 0.060 (1.52) MAX 0.210 (5.33) MAX 0.150 (3.81) 0.130 (3.30) 0.115 (2.92) 0.015 (0.38) GAUGE PLANE SEATING PLANE 0.005 (0.13) MIN 1 0.430 (10.92) MAX 0.014 (0.36) 0.010 (0.25) 0.008 (0.20) 0.320 (8.13) 0.290 (7.37) 0.405 (10.29) MAX 0.060 (1.52) 0.015 (0.38) 0.200 (5.08) MAX 0.150 (3.81) MIN 0.200 (5.08) 0.125 (3.18) 0.023 (0.58) 0.014 (0.36) 0.070 (1.78) 0.060 (1.52) 0.045 (1.14) 4 0.100 (2.54) BSC 0.195 (4.95) 0.130 (3.30) 0.115 (2.92) 0.015 (0.38) MIN 0.022 (0.56) 0.018 (0.46) 0.014 (0.36) 5 0.070 (1.78) 0.030 (0.76) SEATING PLANE 15° 0° 0.015 (0.38) 0.008 (0.20) CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. COMPLIANT TO JEDEC STANDARDS MS-001-BA CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS. 図33.8 ピン・プラスチック・デュアルインライン・パッケージ[PDIP] ナロー・ボディ (N-8) 寸法:インチ(mm) 図34.8 ピン・セラミック・デュアルインライン・パッケージ [CERDIP] (Q-8) 寸法:インチ(mm) オーダー・ガイド Model Temperature Range Package Description Package Option AD708JN AD708JNZ1 AD708AQ AD708BQ AD708SQ/883B 0°C to +70°C 0°C to +70°C −40°C to +85°C −40°C to +85°C −55°C to +125°C 8-Lead Plastic Dual In-Line Package [PDIP] 8-Lead Plastic Dual In-Line Package [PDIP] 8-Lead Ceramic Dual In-Line Package [CERDIP] 8-Lead Ceramic Dual In-Line Package [CERDIP] 8-Lead Ceramic Dual In-Line Package [CERDIP] N-8 N-8 Q-8 Q-8 Q-8 1 Z = 鉛フリー・デバイス。 Rev. C - 13/13 -

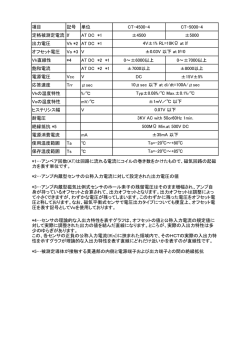

© Copyright 2026