14nm技術、ようやく量産へ ファンドリーの準備も加速か

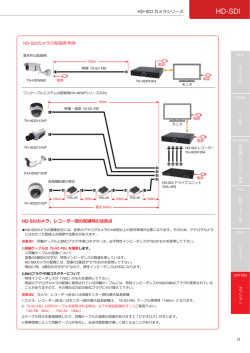

最前線 Silicon Valley の半導体企業 《Intelの14nmプロセス&ファンドリー向け技術》 14nm技術、ようやく量産へ ファンドリーの準備も加速か 服部コンサルティング・インターナショナル 代表 服部 毅(本誌編集顧問) 米Intelは、14nmプロセスを採用した第2世代FinFETおよび最初の14nm MPUの概要を公表し た。ようやく所定の歩留り確保のめどが立ち、計画より約1年遅れで量産を開始する。また、 ファンドリー事業への本格参入の準備も急いでいる。 ●まずはタブレット向け14nm MPUから出荷 米Intelは9月、14nmプロセスを採用したMPUの 最初の製品「Core M」 (開発コード名「Broadwell-Y」 ) の概要を正式発表した。14nm プロセス技術は、 Intelが22nmから導入したFinFET(Intelは「トライ ゲートトランジスタ」と呼んでいる)のいわば第2 世代版である。Core MはBroadwell世代のMPUのう ち、2 in 1タブレットPC(ディスプレイ部とキーボ ード部を分離し、ディスプレイ部をタブレットと して使えるPC)に向けたモデルであり、ファンを 用いずに数Wで操作できるように設計されている。 このタブレットPCは年末商戦に間に合わせたいと しているが、本格的なPC向けは来年にずれ込む。 Intelは今後順次、14nm製造技術をスーパーコン (a)Fin構造の模式図 ピュータに向けた高性能プロセッサからIoT(Internet of Things)端末に向けた超小型低消費電力MPU まで、幅広く適用していく方針だ。 事前に予想した通り 1)、Intelは第2世代FinFETで は背高フィン(Tall Fin)を採用して、電流駆動能 力を向上させた。具体的には、フィンの高さを第1 世代(22nmプロセス)の34nmから42nmへと高く するとともに、フィン間隔を60nmから42nmに狭め、 トランジスタのゲート間隔も90nmから70nmに狭 め、1個のトランジスタに用いるフィンの数を減ら し集積度の向上を図った。多層配線の間隔も狭め、 SRAMメモリセルの面積を半減させた(図1)。同 社は、14nmでもトランジスタ当たりの製造コスト 削減のペースを維持できたとしており、Mooreの法 (b)FinFETのSEM像 42nm pitch 60nm pitch 42nm Height 34nm Height (c)多層配線構造断面のSEM像 80nm minimum pitch (d)メモリセルのSEM像 52nm(0.65×) minimum pitch 0.108μm2 図1 22nmプロセスと14nmプロセスの比較( (a)∼(d)でそれぞれ左が22nm、右が14nm) 54 Electronic Journal 2014 年 10 月号 0.0588μm2 (出所:Intel) 最前線 Silicon Valley の半導体企業 化を図ることに全力 を挙げて取り組んで いるので 14nm から は当社の方が高密度 化で勝る」と述べた。 ●ファンドリー事業 で2.5次元実装技 術を導入 Intelは、ファンド リー事業への本格参 (a)2013年11月公表 (b)2014年8月公表 入の準備を着々と行 っており、8 月にフ 注:22nmが所定の歩留りに到達した時期を14nmの所定歩留り到達予定時期に揃えて表記しているため、 横軸の時期は22nmには適用されない。また、縦軸の尺度は正確ではなく、両図の尺度は異なる ァンドリー事業の顧 図2 14nm MPUの歩留り推移 (出所:Intel) 客に提供する2つの 新技術を発表した。 則は未だ終焉を迎えていないことを強調している。 「Embedded Multi-die Interconnect Bridge(EMIB)」 と呼ばれる2.5次元パッケージング技術と、「High Density Modular Test(HDMT)」と呼ばれるテスト ●14nmは計画より1年遅れで量産開始へ 技術である。これらの技術を使用することで実装 Intelの当初の計画では、14nm MPUは2013年中に 工程やテスト工程のコストを低減できるという。 量産を開始するはずだった。しかし、昨年10月に EMIBは、14nmプロセスを利用する顧客向けに、 Krzanich CEOは、「試作時の欠陥密度が高く、所定 同一パッケージ内で異種チップを高密度に接続す の歩留りが確保できないため、量産開始を2014年 る技術。異種チップ同士をつなぐ小さなブリッジ 第1四半期に延期する」と発表した 2)。昨年11月に チップを挿入することで、異種チップ間の必要な はアナリストに対して図2(a)のような歩留り推 箇所だけを高密度に接続できる。このパッケージ 移グラフを示して、歩留りが暴れるトラブルを乗 り越えて2014年初頭には量産できると胸を張った。 ング技術では、標準的なフリップチップ実装を使 しかし、残念ながら歩留りはその後も低迷した。 っているので、安定した電源供給ができ、チップ とパッケージ基板の間で高速信号を直接やりとり 最新の情報(図2(b) )によると、歩留りは向上し できる。同社は、コスト低減と製造工程簡素化を つつあるが、本格量産は来年になりそうだ。年末 最優先で取り組んだため、高コストのTSVを用い 商戦用チップは米国オレゴン州の14nm試作ライン た3次元実装やSiインターポーザ(TSV応用技術で (D1X Module 1)から出荷する。すでに、450mm高コスト)を用いた2.5次元実装を採用を見送った。 compatible 300mmファブとして竣工しているアリゾ 一方、HDMTはこれまでは自社製品のみに適用 ナ州の14nm量産ライン(Fab 42)で年内にも量産を してきたハードウェアとソフトウェアのモジュー 開始し、アイルランドのFab 24では来年量産を始め ルを組み合わせたテストプラットフォームである。 るという。 少量品から量産まで同一のプラットフォームで対 14nmプロセスを用いた製品の量産開始が1年遅 応できることから、製品の開発期間短縮や生産性 れてしまった点に関して、Intelシニアフェローの 向上に寄与するとしている。EMIBは2015年に顧客 Mark Bohr氏は、「積極的にゲート間隔とフィン間 がサンプル出荷する製品から利用可能となり、 隔を縮小したため歩留りの面で問題が生じてしま HDMTについては、直ちに提供を開始する。 ったが、今は回復しつつあり、今後も改善を図っ ていく」と述べた。さらに、「他社が第1世代のFin参考文献 FETを出荷する前に、当社はすでに第2世代のFin1)服部毅:Electronic Journal 2014.8. p17 FETの出荷に向けて準備を進めている。従来のプレ 2)服部毅:Electronic Journal 2013.11. p.23 ーナ構造のトランジスタでは、他社は高密度化に 優れていたが、当社は以前と同じペースで高密度 Electronic Journal 2014 年 10 月号 55

© Copyright 2026